# 存储器IC的应用技巧

## UV-EPROM/EEPROM/SRAM/DRAM 的结构与使用方法

[日]桑野雅彦 著

王庆资

钱 城 刘涓涓 校

## 目录

#### 第1章 UV—EPROM 的结构与使用方法

- 1.1 UV—EPROM 的结构与特征

- 1.1.1 UV—EPROM 的单元结构

- 1.1.2 UV—EPROM 的写入与擦除

- 1.1.3 一次性 PROM

- 1.2 UV─EPROM 的输入输出信号

- 1.3 操作模式

- 1.3.1 数据读(Data Read)

- 1.3.2 输出禁止(Output Disable)

- 1.3.3 待机(TTL/CMOS)

- 1.3.4 编程(Programming)

- 1.3.5 编程验证(Program Verify)

- 1.3.6 编程禁止(Program Inhibit)

- 1.3.7 自动选择(Auto Select)

- 1.4 DC 规定

- 1.5 UV─EPROM 的读操作

- 1.6 UV—EPROM 的编程方法

- **1.6.1 UV-EPROM** 写入方式的变迁

- 1.6.2 Am27C010 的编程方法

- 1.6.3 UV—EPROM 擦除器的制作

#### 第2章 闪速存储器的结构与使用方法

- 2.1 闪速存储器的概要

- 2.2 闪速存储器的分类及特征

- 2.3 NAND 闪速存储器

- 2.3.1 TC58V64 的引脚配置

- 2.3.2 NAND 闪速存储器的内部结构

- 2.3.3 操作指令

- 2.4 NOR 闪速存储器

- 2.4.1 引脚配置

- 2.4.2 信号的种类

- 2.4.3 与处理器的连接实例

- 2.4.4 读周期的概要

- 2.4.5 写周期的概要

- 2.4.6 读周期的时序

- 2.4.7 写周期的时序

- 2.4.8 闪速存储器指令

#### 第3章 EEPROM 的结构与使用方法

- 3.1 EEPROM 的概要

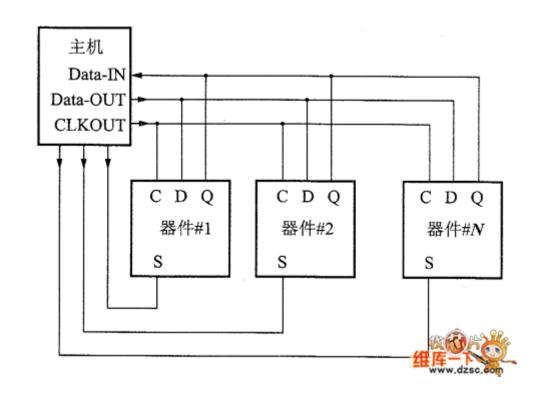

- 3.2 串行 EEPROM

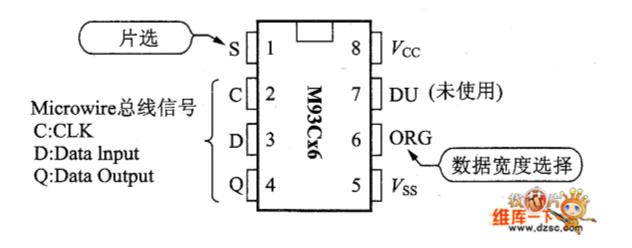

- 3.3 Microwire 总线对应的存储器——M93Cx6

- 3.3.1 M93Cx6 的引脚配置

- 3.3.2 Microwire 总线的存取操作

- 3.4 SPI 总线存储器——M95256

- 3.4.1 M95256 的引脚配置

- 3.4.2 SPI 总线对应的存储器的操作

- 3.4.3 指令设置

- 3.4.4 状态寄存器

- 3.5 **I**<sup>2</sup>C总线对应的存储器──M24CXX

- 3.5.1 I<sup>2</sup>C总线与串行EEPROM

- 3.5.2 I<sup>2</sup>C总线存储器M24C01—M24C16

- **3.5.3 I**<sup>2</sup>C总线的基本操作

- 3.5.4 写操作的流程

- 3.5.5 读操作的流程

- 3.5.6 扩展I2C总线存储器

- 3.5.7 M24C64 的时序

- 3.6 并行 EEPROM

- 3.6.1 M280IO 的信号

- 3.6.2 基本的存取操作

- 3.6.4 状态寄存器

#### 第4章 SRAM 的结构与使用方法

- 4.1 SRAM 的单元结构

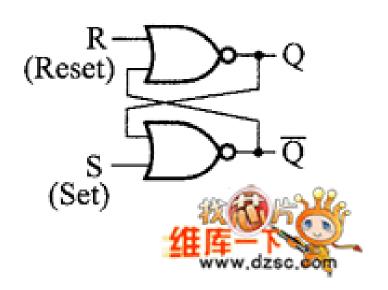

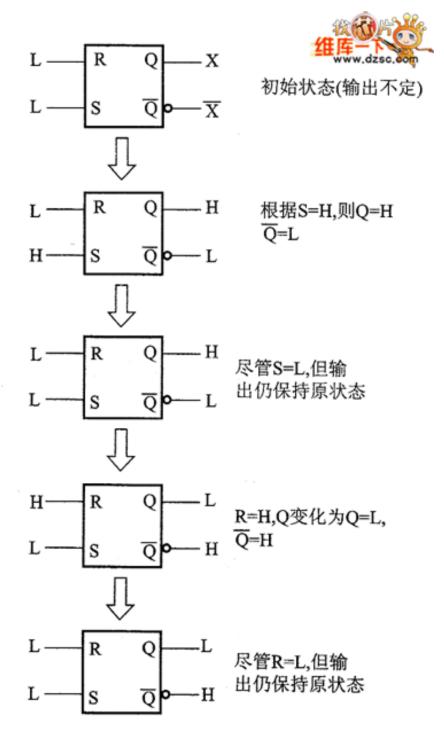

- 4.1.1 RS 触发器

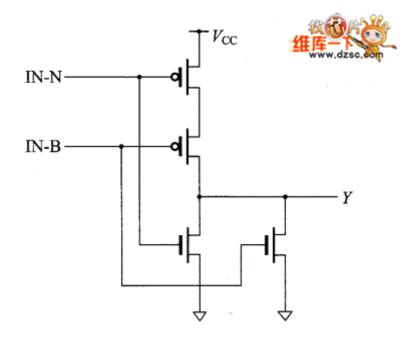

- 4.1.2 4 晶体管单元

- 4.1.3 6 晶体管单元

- 4.2 SRAM 的分类

- 4.2.1 异步 SRAM

- 4.2.2 同步 SRAM

- 4.2.3 双端口 SRAM

- 4.2.4 FIFO

- 4.3 异步 SRAM

- 4.3.1 异步 SRAM 的信号

- 4.3.2 异步 SRAM 的基本操作

- 4.3.3 时序的解析

- 4.4 同步 SRAM

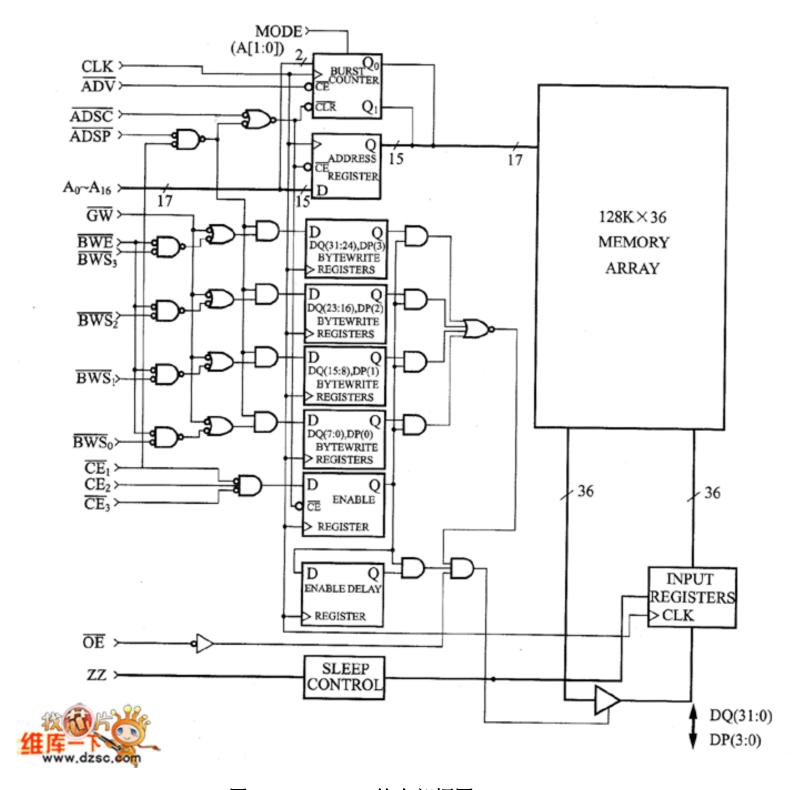

- 4.4.1 同步管道突发式 SRAM

- 4.4.2 实际的同步管道突发式 SRAM

- 4.4.3 同步管道突发式 SRAM 的各种信号

- 4.4.4 同步管道突发式 SRAM 的基本操作

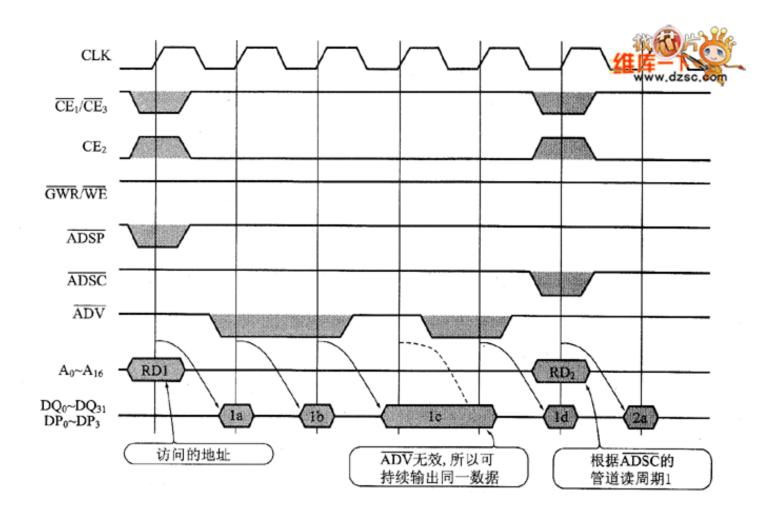

- 4.4.5 同步突发式 SRAM

- 4.4.6 实际的同步突发式 SRAM

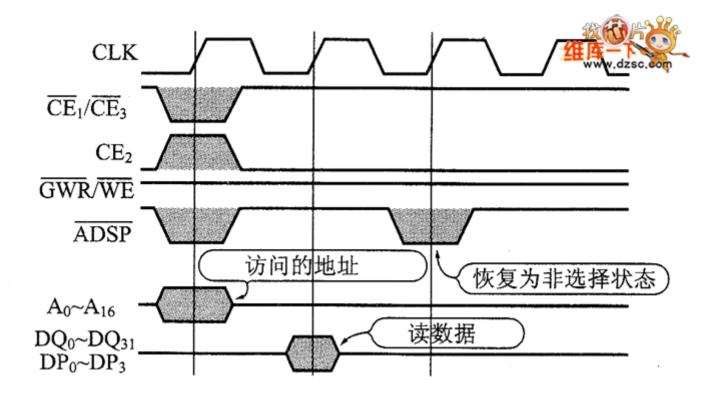

- 4.4.7 同步突发式 SRAM 的单一读操作

- 4.4.8 同步突发式 SRAM 的突发读操作

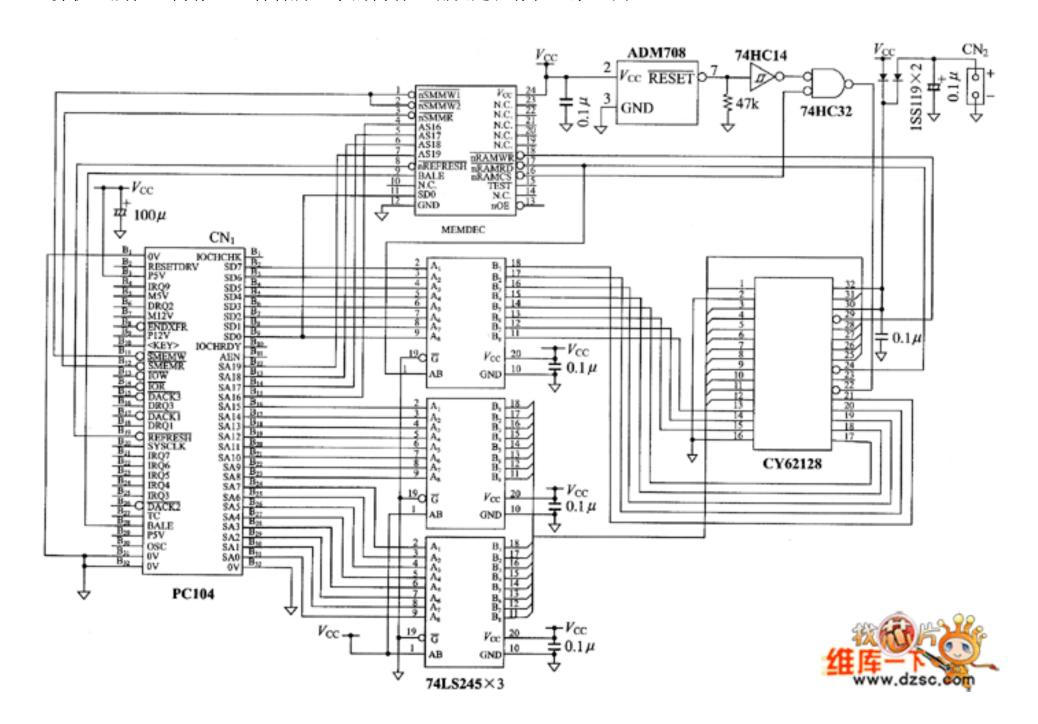

- **4.5 SRAM** 主板的制作

- 4.5.1 ISA 总线存储器周期的注意事项

- 4.5.2 SRAM 存储器主板的基本设计

- 4.5.3 SRAM 存储器主板的操作确认

#### 第5章 特殊的 SRAM 的结构与使用方法

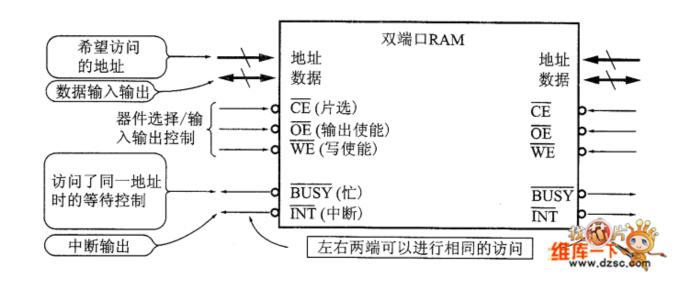

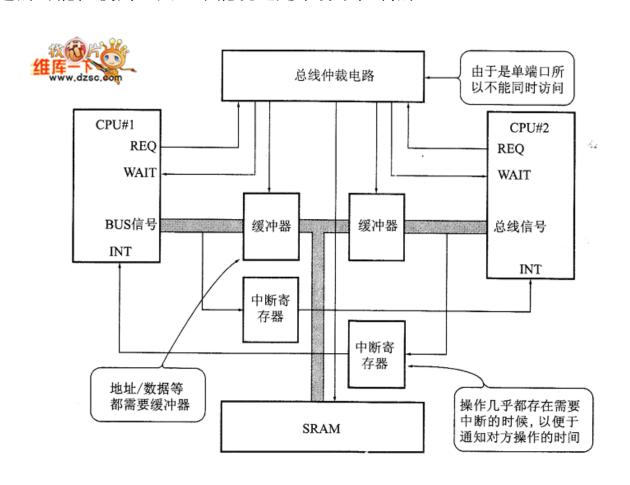

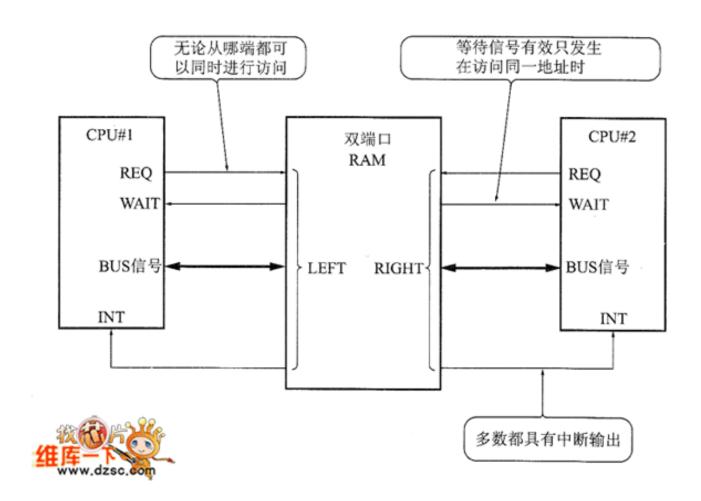

- 5.1 双端口 **SRAM**

- 5.1.1 异步类型的双端口 SRAM

- 5.1.2 CY7CO19 的引脚配置

- 5.1.3 CY7CO19 的信号线

- 5.1.4 CY7CO19 的基本操作功能

- 5.1.5 同步类型的双端口 SRAM

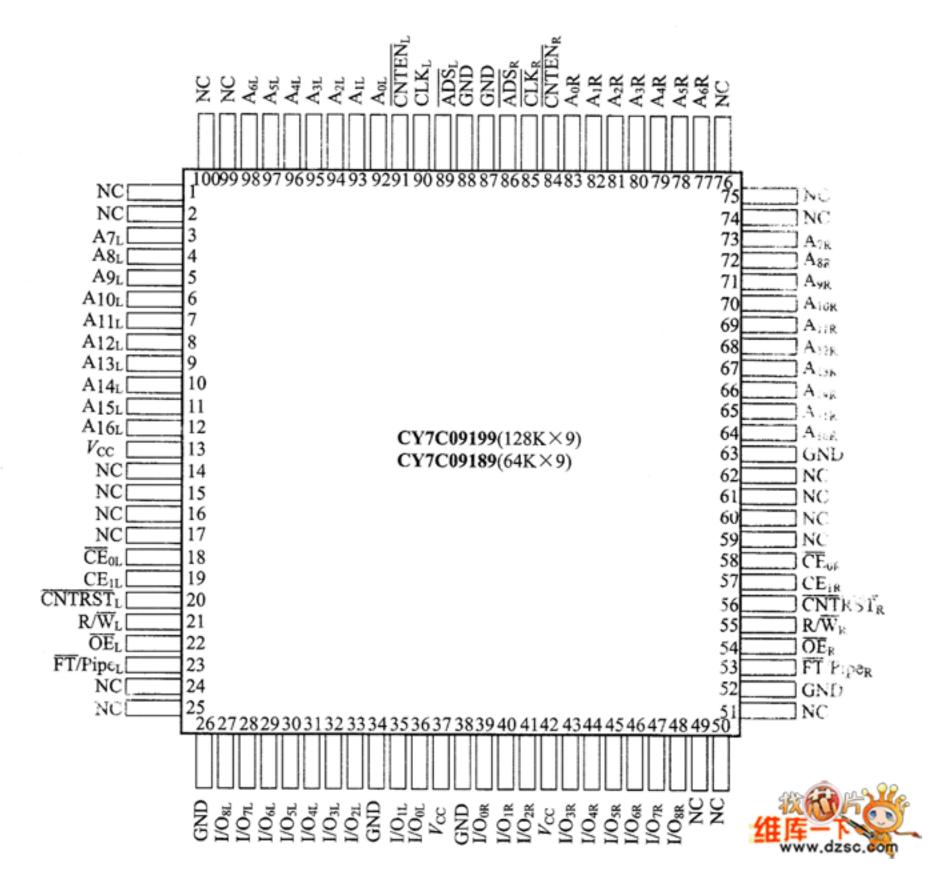

- 5.1.6 CY7CO9199 的引脚配置

- 5.1.7 CY7CO9199 的信号

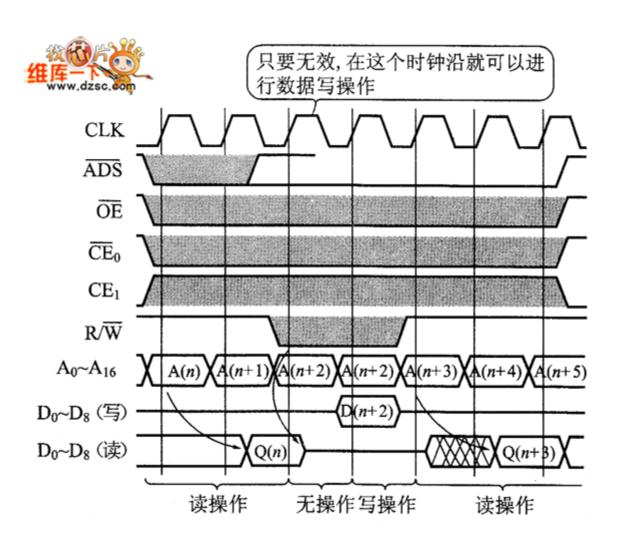

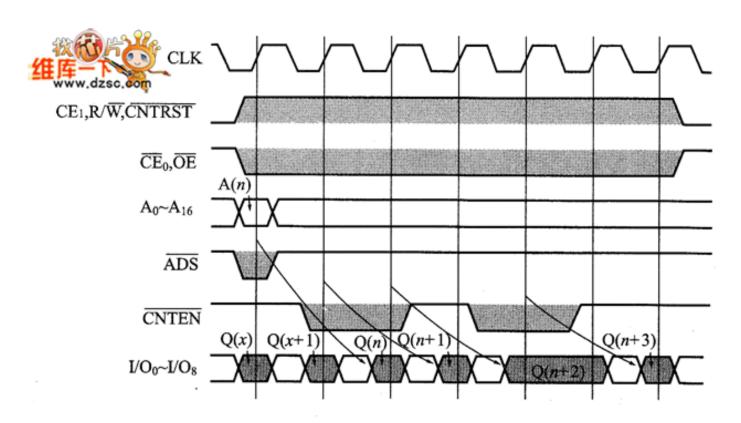

- 5.1.8 CY7C09199 的存取操作

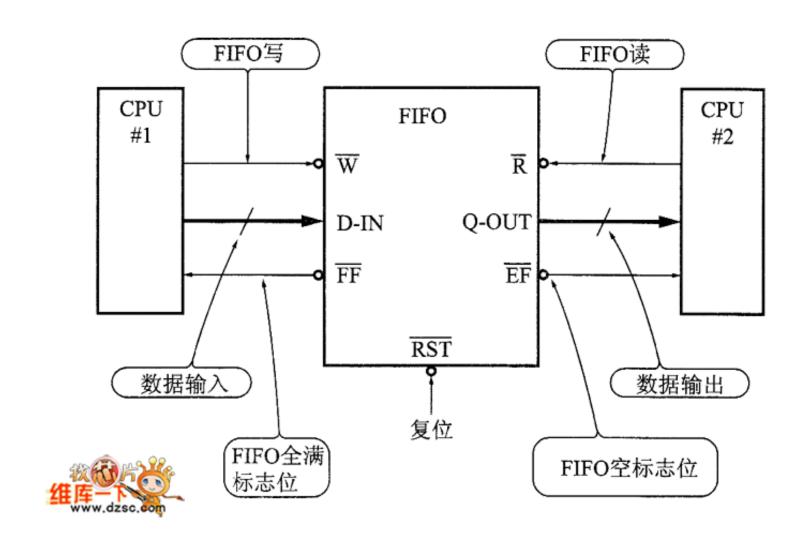

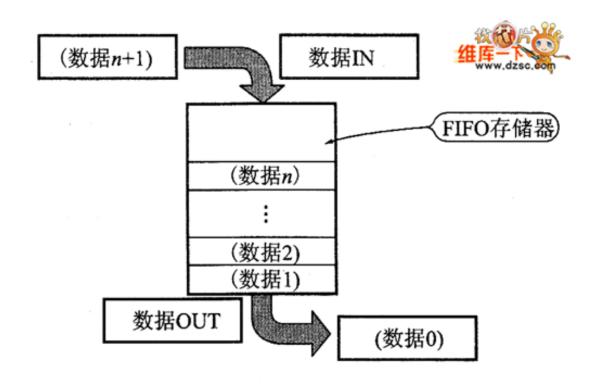

- 5.2 FIFO 存储器

- 5.2.1 实际的 FIFO 存储器

- 5.2.2 CY7C419 的信号

- 5.2.3 CY7C419 的操作

#### 第6章 DRAM 的结构与使用方法

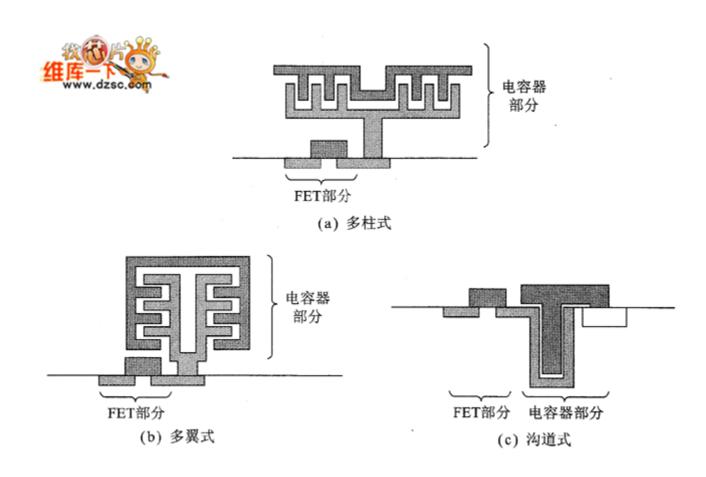

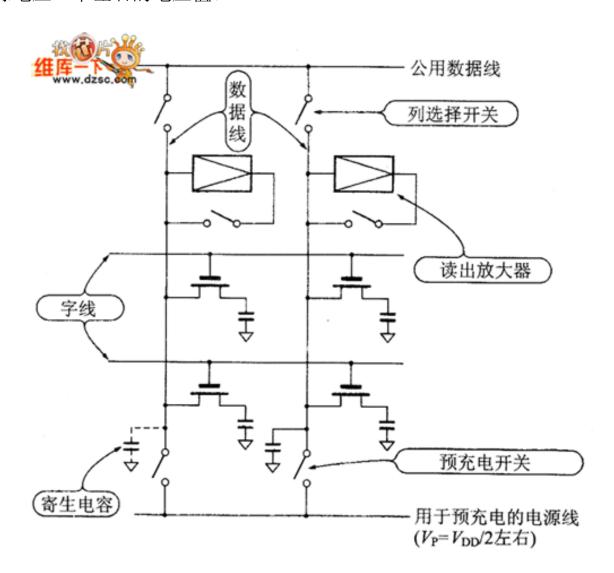

- 6.1 DRAM 的单元结构

- 6.1.1 DRAM 单元结构的概况

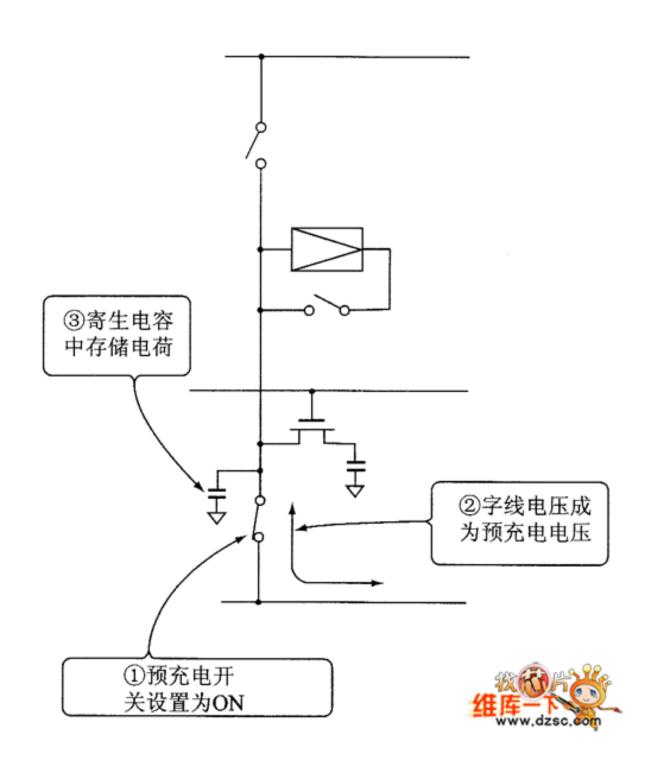

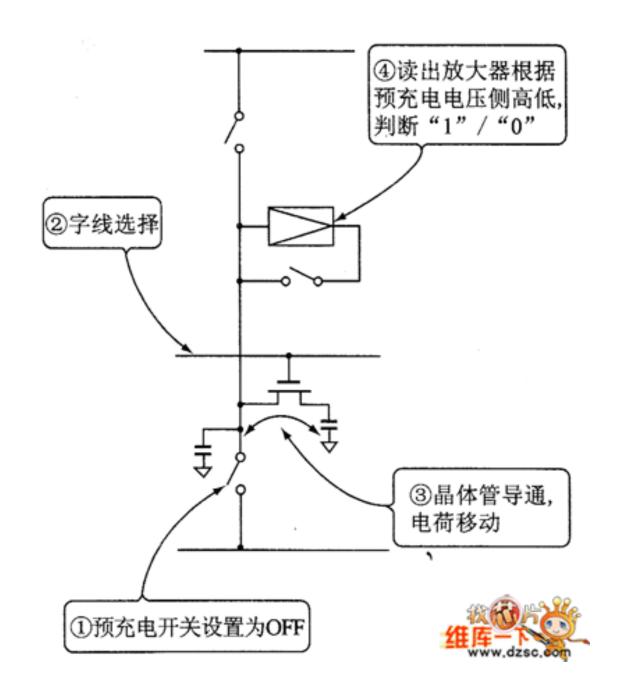

- 6.1.2 刷新

- 6.1.3 软错误

- 6.1.4 电容器的设计

- **6.2 DRAM** 内部电路

- 6.3 DRAM 的外部接口

- 6.3.1 DRAM 的基本信号

- 6.3.2 DRAM 的读 / 写操作

- 6.3.3 DRAM 的刷新操作

- **6.3.4 DRAM** 的快速访问模式

- 6.4 同步 DRAM

- 6.4.1 同步 DRAM 的信号

- 6.4.2 SDRAM 指令

- 6.4.3 同步 DRAM 的存取操作示例

- 6.5 DDR—SDRAM

- 6.5.1 DDR—SDRAM 的信号

- 6.5.2 DDR—SDRAM 的操作

- 6.6 直接总线式 DRAM

- 6.6.1 直接总线式 DRAM 的信号

- 6.6.2 直接总线式 DRAM 的信号连接

- 6.6.3 直接总线式 DRAM 的操作概况

- 6.6.4 直接总线式 DRAM 的操作示例

## 存储器 IC 的应用技巧

## 第一章

## UV-EPROM 的结构与使用方法

## 1.1 UV-EPROM 的结构与特征

## ●1.1.1 UV - EPROM 的单元结构

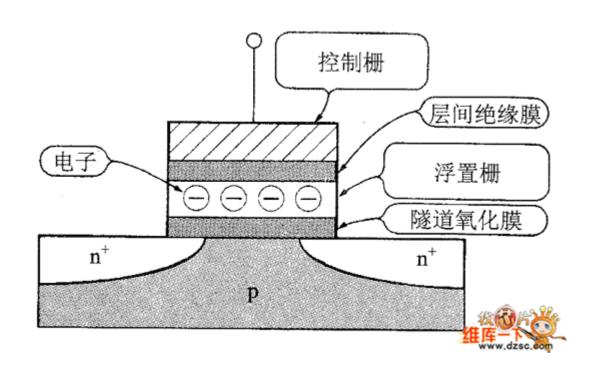

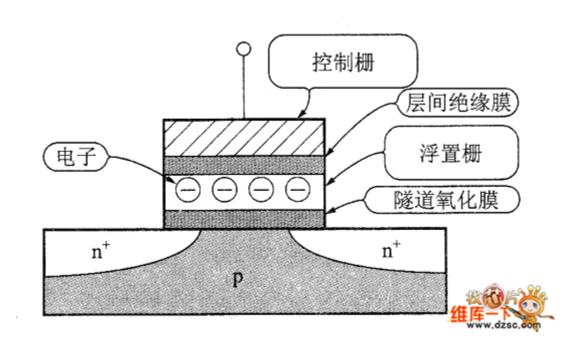

UV-EPROM的单元结构如图所示。其基本结构与在下一章中说明的闪速存储器相同。UV-EPROM的存储单元是由MOSFET(金属氧化物半导体场效应晶体管)构成的,在它的控制栅和N沟道间有一个称为浮置栅的特殊栅极,这是UV-EPROM单元结构的主要特征。

图 UV-EPROM 的单元结构

由于浮置栅利用氧化膜使栅极与基板绝缘,使存储于此处的电荷不能被轻易释放,从而达到持续保存记忆的目的。与闪速存储器相同,通过浮置栅中是否存储电荷,利用 FET (场效应晶体管)的阈

值电压的变化,进行高电平与低电平的判断。一般地讲, UV 一 EPROM 在擦除状态(浮置栅中未存储电荷的状态)时,读出"高电平";而在存储电荷状态时,读出"低电平"。

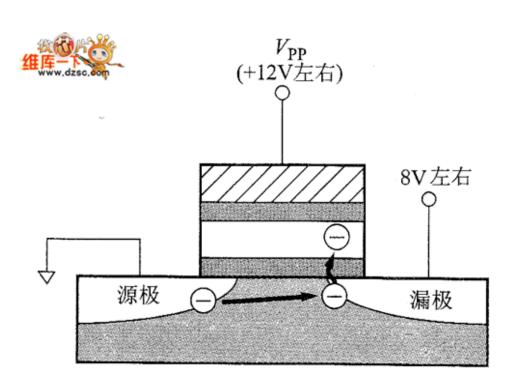

## ● 1.1.2 UV - EPROM 的写入与擦除

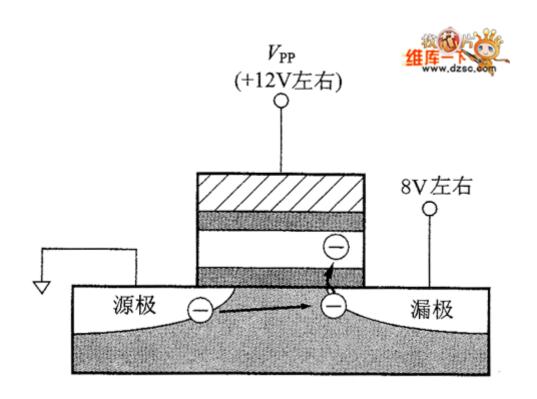

写入时,通过给栅极加上高电压 vPP,如图 1 所示,向浮置栅注入电荷。注人后的电荷由于不具备穿透硅氧化膜能壁的能量·因而只能维持现状。

图 1 UV-EPROM 的写入

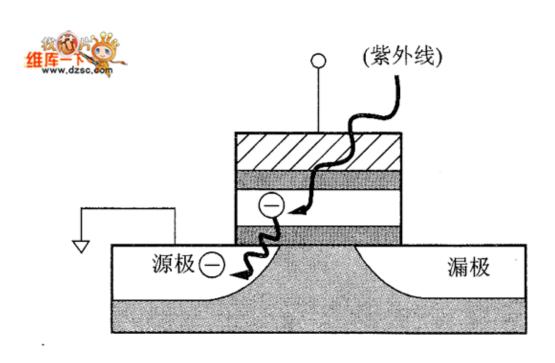

当浮置栅接收到紫外线的照射,浮置栅中的电子接收了紫外线光量子的能量,则电子变成具有穿透硅氧化膜能壁能量的热电子。如图 2 所示,热电子穿透硅氧化膜,流向基板和栅极,恢复为擦除状态。UV-EPROM 的擦除操作,只能通过接收紫外线的照射来进行,而不能进行电子擦除。也就是说,UV-EPROM 只能够进行由"1"向"0"改变比特数,而在反方向上. 除擦除芯片全部内容的方法以外,再没有其他的方法。

图 2 UV-EPROM 的擦除

我们知道,光的能量与光的波长成反比例关系,为了让电子成为热电子,从而具有穿透氧化膜的能量,就非常需要波长较短的光即紫外线的照射。由于擦除时间决定于光量子的数目,因而即使在波长较短的情况下,也不能缩短擦除时间。一般地,当波长为 400OA(400nm)左右时才开始进行擦除。在3000A左右基本达到饱和。低于 3000A以后,波长即使再短,对于擦除时间也不会产生什么影响。

UV-EPROM 擦除的标准一般为接受波长 2537A、12 000μW / cm2 的紫外线 15~20 分钟左右的照射,即可完成其擦除操作。

根据擦除机制可知,即使得到热能,浮置栅电荷的消失也是发生在某一概率下。其发生的概率是随着器件绝对温度的上升以指数函数递增的。

#### ● 1.1.3 一次性 PROM

UV-EPROM为了实现紫外线擦除功能而在封装的中心部位设置了能看到芯片的窗口。如果去掉该窗口的设置,而改为廉价的塑料封装,则不具各擦除(比特由"0"返回"1")功能,这就是PROM。在将UV EPROM做为产品加以利用时,为防止紫外线照射而擦除数据,一般都在窗口部位贴上遮光片。不同的产品一般写入数据、且擦除后再次利用的情况较少。针对这样的用途,起初就不设置窗口的一次性PROM则具有较大的优势。因为UVEPROM与一次性PROM除封装不同之外,内在机制是完全相同的。所以,ROM写人器的自动识别功能会将这两种类型的器件作为同一类型进行处理。这样,在产品试制期间,可以利用UV-EPROM进行实验。而在制造产品时,则可以顺利地以一次性PROM取代UV-EPROM,这对于产品的生产是非常有利的。

## 1.2 UV-EPROM 的输入输出信号

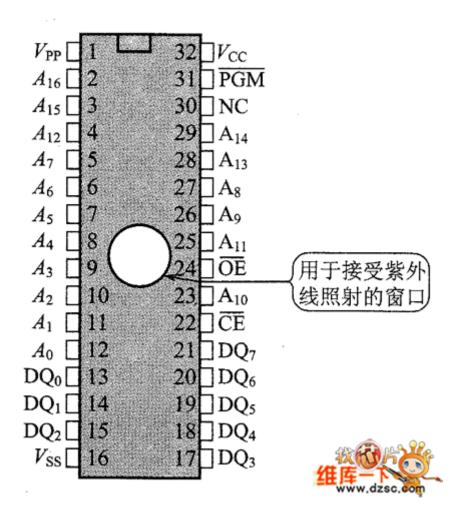

作为UV-EPROM的实例,我们以AMD公司 1M位(128K×8 位)UV-EPROM的Am27C010为例进行说明。

Am27C010 的引脚配置如图 1 所示,图 2 是在其内部框图的基础上,根据引脚的功能分组表示的。在图 1 中,NC引脚没有在图 2 中出现,NC是无连接(No-Connection)的缩写,它虽然作为封装的引脚存在,但其内部并不与任何部件相连接。下面我们逐一说明这些引脚所代表的意思。

图 1 Am27C010 的引脚配置

图 2 Am27C010 的内部框图

#### ▲ A0~A16 (地址总线)

A0~A16 为地址总线。因为 Am27C010 是 128K×8 位结构的 1M 位的 UV-EPROM,所以地址有 128K、17 根总线。通常 A0 作为 LSB(最低位比特)、A16 作为 MSB(最高位比特)使用。 RAM 由于只需要读出与写入时相同的内容,所以即使 A15 与 A16 反向连接也无所谓。而 UV-EPROM

由于写入时使用了 ROM 写入器,因而引脚的顺序几乎就不能替换进行使用(考虑软件解析的方法,有意替换地址来加以利用的例子也存在)。

作为特殊用途的 A9 引脚通过赋予+12V 的电压,可使其读出制造商名称以及器件的 ID 编码。 这应用于 ROM 写人器自动判断插座上所插接的 ROM 类别上,在普通的系统中这样的功能很少用。

#### ▲ DQ0~DQ7 (数据总线)

DQ0~DQ7是数据总线。由于Am27C010为128K×8位的结构,因而数据线也具有8位的宽度。与地址总线相同,数据总线虽然为了破解困难也存在有意使用非标准的情况,但通常情况下,将DQ0作为LSB,DQ7作为MSB使用。在一般的操作中,UV-EPROM为ROM,即只读存储器,所以DQ0~DQ7为输出专用引脚,只在编程时用于输入。

#### ▲ /OE (输出使能, Output Enable)

/OE是ROM数据输出缓冲器的使能信号,是低电平激活的输入引脚。当与CS一起为有效信号(为低电平)时,向地址总线(A0~A16)所指定的地址中写人的数据将出现于数据总线(DQ0~DQ7)上。另外,本书在表示低电平激活的情况下,信号名上一般标有上划线。但根据产品不同,有时也在前面或者后面加上斜杠(/),或者类似OE#那样在后面加上#的记号。

#### ▲ /CE (芯片使能, Chip Enable)

根据产品的不同,该引脚有时也为CS(芯片选择,简称片选,Chip Select),这是将器件设置为选择状态的信号,通常与/OE共同应用于数据读出中。

#### **▲** /PGM (编程使能)

应用于编程(写入)中,在**Vpp**端口加上编程电压(+12**V**)的状态时是有效信号。除此之外, 在一般的操作中该引脚没有任何意义。

#### ▲ Vcc (电源输入)

这是用于UV-EPROM工作的电源。一般情况下,装入系统进行操作时,在此赋予+5V的电压。 编程工作时,Vcc也需要赋予电压。

#### ▲ VPP (编程电源输入)

这是编程时提供编程电压(+12V左右)电源的引脚,利用该电压向浮置栅注人电荷。在最近的闪速存储器等器件中,大多在芯片内部都具各升压电路,由Vcc所提供的电压生成擦除/编程电压。但是UV-EPROM由于不需要进行在板写人,所以没有内置升压电路,而是在编程时由ROM写人器提供电源。

Am27C010 在进行普通的读操作时,虽然忽略了VPP,但根据UV-EPROM的特性,有时也需要给VPP提供与Vcc相同的电压。这样的数据最好参看关于UV-EPROM的数据手册。

#### ▲ GND (地线)

这是器件确定电压基准的引脚,所有输入输出信号电压的规定都是以该引脚为标准的。

## 1.3 操作模式

Am27C010 的操作是由 CE、OE、PGM 等输入信号的状态决定的。操作模式与各种引脚状态的关系 如表所示。系统使用的一般为数据读、输出禁止、待机三种模式。

| 操作模式          | CE                   | ŌĒ  | PGM | A <sub>0</sub> | $A_1 \sim A_8$ | A9          | $A_{10} \sim A_{16}$ | $V_{ m PP}$       | $DQ_0 \sim DQ_7$          |

|---------------|----------------------|-----|-----|----------------|----------------|-------------|----------------------|-------------------|---------------------------|

| 数据读           | "L"                  | "L" | "X" | "X"            | "X"            | "X"         | "X"                  | "X"               | 数据输出                      |

| 输出禁止          | "L"                  | "H" | "X" | "X"            | "X"            | "X"         | "X"                  | "X"               | 高阻抗                       |

| 待机(TTL)       | "H"                  | "X" | "X" | "X"            | "X"            | "X"         | "X"                  | "X"               | 高阻抗                       |

| 待机(CMOS)      | $V_{\rm CC}\pm$ 0.3V | "X" | "X" | "X"            | "X"            | "X"         | "X"                  | "X"               | 高阻抗                       |

| 编 程           | "L"                  | "H" | "L" | "X"            | "X"            | "X"         | "X"                  | $V_{	ext{PP}}$    | 数据输入                      |

| 编程验证          | "L"                  | "L" | "H" | "X"            | "X"            | "X"         | "X"                  | $V_{	ext{PP}}$    | 数据输出                      |

| 编程禁止          | "H"                  | "X" | "X" | "X"            | "X"            | "X"         | "X"                  | $V_{\mathrm{PP}}$ | 高阻抗                       |

| 14 73k Mr 107 | "L"                  | "L" | "X" | "L"            | "L"            | $V_{\rm H}$ | "L"                  | "X"               | 制造商代码<br>(Am27C010 为 01h) |

| 自动选择          | "L"                  | "L" | "X" | "H"            | "L"            | $V_{\rm H}$ | "L"                  | "X"               | 器件代码<br>(Am27C010 为 0Eh)  |

表 Am27C010 的操作模式

\*: VPP = 12.75V ± 0.25V, VH = 12.0V ± 0.5V, "X": 无论何信号都无关紧要

在表中,"H"代表 VIH(+2.0V以上),"L"代表 VIL(+0.8V以下), VIH与 VIL分别决定了其电压的上限和下限,Am27C010的 VIH上限为 Vcc+0.5V, VIL下限为一0.5V(以 GND 引脚为基准)。如果端口加上超过该范围的电压,则器件有可能会毁坏。

### ● 1.3.1 数据读 (Data Read)

这是读取ROM内容的操作。一旦/CE有效(低电平),则芯片处于使能(选择)状态,通过使/OE有效,向外部输出ROM内容的输出缓冲器将处于使能状态。利用 17 根地址总线(A0~A16),在128KB中指定所希望读出的那个比特位。

如果在这种状态下等待数据的读出,则DQ0~DQ7 中将出现数据,外部电路的CPU将提取这些数据进行操作。因为并没有利用/PGM及VPP端口,所以无论是高电平还是低电平都无关紧要。关于读操作的细节我们将在后面进行叙述。

## ●1.3.2 输出禁止(Output Disable)

由于/CE有效,所以芯片本身处于使能状态,但是根据/OE,输出缓冲器将处于禁止状态。因为只要稳定地址总线,使/CE有效,就可以针对ROM内部的存储器单元进行访问,所以在输出禁止模式下,首先进行内部操作,然后使/OE有效,这样一旦进人数据读模式,就可以缩短表面上的存取时间。

采用下面这种连接方法的情况较多,即当 ROM 连接在比读控制信号先确定的地址上时,地址的低位与 ROM 连接,对高位进行解码生成/CE 信号,然后将读信号传人/OE。在这种情况下的 ROM 操作,实际上是由输出禁止模式向数据读模式的转移。

## ●1.3.3 待机 (TTL/CMOS)

/CE一旦变为高电平,则UV-EPROM处于非选择状态。此时,根据/CE的电压,损耗电流将逐渐改变。当/CE是一般的高电平(+2.0V以上)时,处于TTL待机状态。尽管如此,但如果CE进而增高到Vcc±0.3V,则UV-EPROM处于CMOS待机状态,损耗电流就会变得更小。Am27C010的TTL待机电流最大为1.0mA,而其CMOS待机时的电流为100μA,减小了一个数量级。

随着CMOS器件各种形式组合的逐渐增多,有时侯会在无意识的情况下使器件处于CMOS待机状态。 最近,器件的电源电压一般都被降低到3.3V以下。如果这种器件的输出与Am27C010 连接,则可以在TTL 待机状态下进行操作。

## ●1.3.4 编程 (Programming)

这是写入操作,但并不只是单纯处于这种状态即可完成操作。由于规定了额定电压以及额定时间,因此编程操作是相当麻烦的。在闪速存储器中,由于时序控制是在器件内部的电路中自动进行的,所以主机方面只要发布指令就可以了。而UV-EPROM的时序控制等所有操作都必须来自外部电路。

### ●1.3.5 编程验证 (Program Verify)

这是用于编程时检查写入是否正确的读出模式。在类型较旧的 EPROM 中,是通过单一的长脉冲进行写人操作的,但由于操作时间过长,所以现在的 EPROM 都采用新的方法,即给予短脉冲进行编程,读出的数据如果与写人的数据一致,则进行下一地址的数据写入。

编程中该数据读出的操作称为编程验证。使/PGM 无效(高电平),只要/OE 有效,就可以进行编程验证操作。

## ●1.3.6 编程禁止 (Program Inhibit)

即使处于加载了 $V_{PP}$ 电压的状态下,一旦/CE为高电平,EPROM也将成为非选择状态,这样的状态是编程禁止模式。使之处于该状态,譬如增加 $V_{PP}$ 电压,这时即使/PGM有效,也不可能误写人数据c该编程禁止模式应用于向编程操作移动之前以及退出编程操作的时候。

## ●1.3.7 自动选择 (Auto Select)

这里并不是指EPROM被自动选择,而是指当ROM写入器判断器件的制造商及型号时,自动选择ROM的容量及编程算法。不添加Vpp电压,在给Ao引脚加上+12V电压的状态下,如果/CE和/OE有效,则可以读出制造商代码(Manufacture Code)和器件代码(Device Code)。由Ao选择读出哪个编码。

## 1.4 DC 规定

电源电压以及输入输出电压等是由DC Characteristic(直流特性)规定的。Am27C010的DC规定 如表所示。该表中经常出现的V<sub>H</sub>等表示方法基本上是这样规定的: 开头第1个字母V表示额定电压, I 表示额定电流; 第2个字母的0表示输出, I表示输人, L表示漏电流或者负载电流; 第3个字母的H表示高电平时的规定, L表示低电平时的规定。

| 符号                 | 意思                         | 测定条件                                                                                         | min  | max                | 单位 |

|--------------------|----------------------------|----------------------------------------------------------------------------------------------|------|--------------------|----|

| $V_{\mathrm{OH}}$  | "H"高电平输出电压                 | $I_{\rm OH} = -400 \mu A$                                                                    | 2. 4 |                    | V  |

| $V_{ m OL}$        | "L"低电平输出电压                 | $I_{\rm OL} = 2.1  {\rm mA}$                                                                 |      | 0.45               | V  |

| $V_{ m IH}$        | "H"高电平输入电压                 |                                                                                              | 2.0  | $V_{\rm CC} + 0.5$ | V  |

| $V_{ m IL}$        | "L"低电平输入电压                 |                                                                                              | -0.5 | +0.8               | V  |

| $I_{LI}$           | 输入负载电流                     | $V_{\rm IN} = 0  \mathrm{V} \sim V_{\rm CC}$                                                 |      | 1.0                | μΑ |

| $I_{ m LO}$        | 输出漏电流                      | $V_{\rm OUT} = 0  \mathrm{V} \sim V_{\rm CC}$                                                |      | 5.0                | μΑ |

| T                  | 工作电流                       | $\overline{\text{CE}} = V_{\text{IL}}, f = 10 \text{MHz},$                                   |      | 30                 | mA |

| $I_{\rm CC1}$      | 工作电视                       | $I_{\text{OUT}} = 0 \text{mA}$                                                               |      | 60                 |    |

| $I_{\rm CC2}$      | TTL待机电流                    | $\overline{\text{CE}} = V_{\text{IH}}$                                                       |      | 1.0                | mA |

| $I_{\rm CC3}$      | CMOS 待机电流                  | $\overline{\text{CE}} = V_{\text{CC}} \pm 0.3 \text{V}$                                      |      | 100                | μΑ |

| $I_{\mathrm{PP1}}$ | V <sub>PP</sub> 提供电源(读操作时) | $\overline{\text{CE}} = \overline{\text{OE}} = V_{\text{IL}}, V_{\text{PP}} = V_{\text{CC}}$ |      | 100                | μΑ |

表 Am27C010 的 DC 规定

####

这是对输出电压的规定。EPROM数据输出缓冲器的输出电压如果是高电平,则在接近电源电压(VCC) 之前无条件输出;如果是低电平,则输出电压为零则是其理想输出。但实际上,器件内部由于存在着 某种电阻,输出端电流越大,高电平时的电压输出越低;相反,低电平时的电压输出越高。

测定条件中所表示的电流通过正负号表示电流的方向:负号表示电流由EPROM流向外部的方向,正号表示外部流入EPROM的方向。

####

这是对输入端的电压规定。规定输入多少伏以上的电压必须判断为高电平,多少伏以下的电压必须 判断为低电平。当输入电压值为V<sub>II</sub>和V<sub>II</sub>之间的电压时,由于各种元器件所存在的误差,因而不能够判 断为何种电平。Am27C010 的 $V_{IH}$ 和 $V_{IL}$ 是俗称"TTL电平"的一般值, $V_{IH}$ 为2. 0V以上的值, $V_{IL}$ 为 0. 8V以下的值。

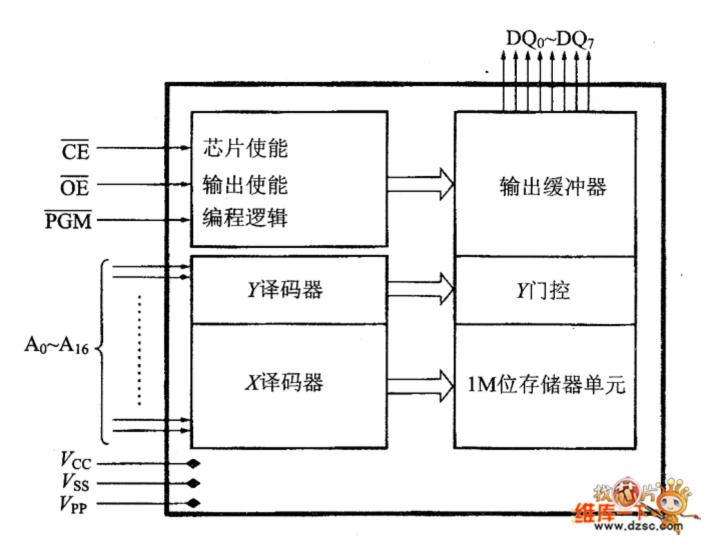

#### $\blacktriangle$ $I_{LI} / I_{LO}$

$I_{\text{II}}$ 是对输人负载电流的规定。由于普通数字IC的基本操作是采用电压的"H(高电平)"、"L(低电平)"的二进制方法,所以理想的情况是如果信号的状态稳定,电流将为零。但现实情况并不是这样的,而是有某种电流流向输入端,该电流就是 $I_{\text{II}}$ ,如图(a)所示。

另一方面, $I_{\text{Lo}}$ 是输出漏电流。输出端为高阻抗,也就是输出开关处于断开状态,理想的情况是无论输出与GND还是与 $V_{\text{CC}}$ 连接都完全没有电流。然而,因为开关元器件的阻抗不是无限大,所以实际上还是有某种电流存在。这就是要规定 $I_{\text{Lo}}$ 的原因,如图(b)所示。

图 I<sub>LI</sub>与I<sub>L0</sub>

即使Am27C010的ILI和ILi值在最大的时候,也不过是 1 µ A和 5 µ A这样小的数值,所以,只要不是大量的器件并联,基本上是不会出现问题的。

#### lack $I_{CC1}$

这是一般操作时的损耗电流。因为数字IC特别是CMOS结构的器件根据操作频率,电流会有较大的变化,所以在此测定条件中标明了操作频率。另外,当输出缓冲器连接有负荷时,电流的流向为Vc端→I/0缓冲器→负载,所以感觉上损耗电流变大。

为了避免这种影响,在 $I_{cci}$ 的测定条件中,将CE置于低电平,使器件处于使能状态;而将0E置为高电平,使输出缓冲器处于禁止状态。在实际的使用条件下,曲于 $I_{cci}$ 值中加上了由缓冲器流向负载的电流,因而需要注意。

另外,由于对于低损耗电流的需求比较多,因此在很多的存储器IC中进行适应Icu值的分类。 Am27C010 也不例外,最大损耗电流为 30mA的与最大损耗电流为 60mA的两种元器件被整合。与其说是制作了不同的产品,不如说是同一产品根据实际测定值或者根据生产计划而改变了用途。

#### $\blacktriangle$ I<sub>CC2</sub>, I<sub>CC3</sub>

这是对待机电流的规定。CE的电压如果超过 $V_{\text{\tiny II}}$ ,则EPROM变为禁止,处于损耗电流较小的待机状态。但GE电压如果增加到 $V_{\text{\tiny CC}}\pm 0.3V$ 左右,则损耗电流将被控制得更小。

Am27C010 通常待机状态(TTL待机)时的电流为 1mA。如果CE的电压处于更高的电压状态(CMOS 待机状态),则此时的待机电流为 100 μ A,降低了十分之一。

#### $lack I_{PP1}$

这是编程时流向VPP端的电流值。V<sub>PP</sub>电压虽然较高,但由于编程时存在存储于浮置栅的电流,因此与 100 μ A相比,该电流值相当小。

## 1.5 UV-EPROM 的读操作

接下来我们看一下UV-EPROM的读操作。无论怎么说,这只是作为ROM(Read Only Memory,只读存储器)的操作,因而非常简单。

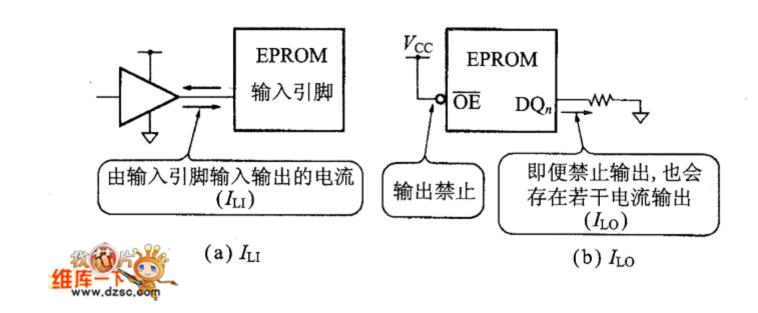

将地址总线(A<sub>0</sub>~A<sub>16</sub>)设置为希望访问的地址,当/CE=/OE=低电平时,DQ中出现数据。

现在,让我们来讨论AC特性。

AC特性对时序进行了规定。图显示了Am27C010 读操作时的波形。具体的时序如表所示。在"速度等级"一栏中虽然有许多内容,但这表示即使是相同的器件,也将根据t<sub>ACC</sub>时间进行区分。器件中标示速度等级的"—45"及"—90"等的数值是与器件型号及批号等一同被打印上去的。

图 Am27C010读操作的波形

| 符号                  |                 |                            | State of the late                      | min/ | Am27C010 速度等级 |     |     |     | 86.6 | 86 C> |      |      |    |

|---------------------|-----------------|----------------------------|----------------------------------------|------|---------------|-----|-----|-----|------|-------|------|------|----|

| JEDEC 式表示           | 一般表示            | 内容                         | 謝定条件                                   | max  | -45           | -55 | -70 | -90 | -120 | -150  | -200 | -255 | 单位 |

| t <sub>AVQ</sub> V  | tACC            | 从地址确定到数据输出<br>为止           | $\overline{CE}$ , $\overline{OE}$      | max  | 45            | 55  | 70  | 90  | 120  | 150   | 200  | 255  | ns |

| telqv               | t <sub>CE</sub> | 从CE有效到数据输出为止               | $\overline{\text{OE}} = V_{\text{IL}}$ | max  | 45            | 55  | 70  | 90  | 120  | 150   | 200  | 255  | ns |

| tGLQV               | toe             | 从OE有效到数据输出                 | $\overline{\text{CE}} = V_{\text{IL}}$ | max  | 25            | 35  | 35  | 40  | 50   | 65    | 75   | 75   | ns |

| t <sub>EHQZ</sub> / | $t_{ m DF}$     | 从CE/OE无效到数据输出高阻抗           |                                        | max  | 25            | 25  | 25  | 25  | 35   | 35    | 40   | 40   | ns |

| taxqx               | tOH             | 地址变化, CE、OE 无效<br>后的数据保持时间 |                                        | min  | 0             | 0   | 0   | 0   | 0    | 0     | 0    | 0    | ns |

表 Am27C010 的 AC 时序

这并不是根据速度等级的不同而进行不同的设计,即使是以完全相同的设计进行制造,也将根据试验结果和出货计划进行等级分类。例如,"-90"器件的 $t_{ACC}$ 最大是 90ns,它不能归类到"-70"的器件中。也就是说, $t_{ACC}$ 的实际测量值如果不是大于 70ns、低于 90ns之间的值,那么根据情况,可能被归类到"-45"及"-70"等的等级中。

下面我们针对图示的时序做少许补充。

▲ t<sub>ACC</sub>: 地址访问时间 (Address Access Time)

在维持/CE=/DE= "L" (低电平) 的状态下,如果改变地址总线的状态,则一定时间后该地址的

数据将显现于DQ端。从地址确定后到数据被实际确定之间的时间就是t<sub>ACC</sub>。在t<sub>ACC</sub>时间形成之前,不能确保DQ端出现数据。

▲ t<sub>CE</sub>: /CE访问时间

在地址确定、/OE仍然维持"L"低电平的状态下,如果/CE有效(为"L"),则一定时间之后将出现指定地址的数据。从/CE有效到确保数据已确定这一段时间是tce。Am27C010的tacc和tce的时间是相同的。

$\triangle$  t<sub>oe</sub>

在地址确定、/CE维持"L"低电平的状态下,从/OE有效到数据被确定的时间就是tom。观察存储器内部,一旦地址确定、/CE有效,则向存储器单元的访问就全部完成,数据输出到EPROM的输出缓冲器前。

在此,只要/OE有效,输出缓冲器就输出数据。为此,比较tacc和tce,toe会更短。

$t_{ACC}$ 、 $t_{CE}$ 和 $t_{OE}$ 无论哪个都不能单独确定大小,必须在整体中去适应速度最慢的那个时间值。例如,在利用了Am27C010 Qn的系统中,地址确定后,在 5ns后/CE有效,再 5ns后/OE有效。从表中可看出, $t_{ACC}$ = $t_{CE}$ =90ns, $t_{OE}$ =40ns。

如果以地址被确定那一时刻作为起点,则:

根据tacc的访问时间: 90ns

根据tc的访问时间: 5ns+90ns=95ns

根据tce的访问时间: 5ns+5ns+40ns=50ns

因而,访问时间的大小取决于t<sub>ACC</sub>、t<sub>CE</sub>和t<sub>OE</sub>中最长的t<sub>CE</sub>,也就是说地址被指定后数据将在95ns后被确定。

$lack t_{ ext{DF}}$

/CE及/OE如果无效,则DQ引脚处于高阻抗状态。但这也不能说是瞬间,还是需要一些时间的,该

时间就是t<sub>IF</sub>。在t<sub>IF</sub>以内的时间里,如果其他的器件驱动了数据总线,则将会与EPROM的输出发生冲突。 因此,在进行硬件设计时必须注意这一点。

#### $\blacktriangle$ $t_{OH}$

提供给EPROM的地址发生变化,或者即使/CE和/OE无效,瞬间数据也不会消失,而是在非常短的时间内,维持输出的原始状态。规定的这个最小时间就是 $t_{cm}$ 。

Am27C010的该时间全部是零,所以不能确保地址发生变化或者/OE及/CE无效后的数据。

## 1.6 UV-EPROM 的编程方法

### ● 1.6.1 UV - EPROM 写入方式的变迁

UV-EPROM 编程的关键在于向浮置栅中注人的电荷,与读操作相比需要非常长的时间,为此一直在进行着写人方式的改善。

从很早期到 64K 位的 EPROM 时期,经常使用的是 50ms 的固定脉冲方式,这是每写人一个地址(1字节)就赋予 50ms 的写脉冲的方式。即使在 64K (8K×8) 位的情况下也需 8K×50ms,即 410s 的时间。如此简单的处理就需要 5分钟以上的时间,显然对于稍微复杂的处理根本不具有实用性。

之后,高速的写人方式出现。这种写入方式是在赋予 1ms 左右的较短的写脉冲的同时,确认数据是否被写入,然后在确认已写人的时刻向下一个地址移动。这种写人方式出现后,写入时间被一下缩短到十分之一的程度。接着,在 1M 位的产品出现之前,还出现了更快的页写入方式等,将脉冲缩短到了 0.2ms 的程度,写脉冲宽度一直减小到使用至今的 50 µ s,是最初 50ms 脉冲的千分之一。

据此,与昔日的64K位的EPROM相比,目前使用的4M位的EPROM写人时间实在是缩短了许多。

EPROM 写人方式与写人时间粗略的推测如表所示。

#### 表 UV-EPROM 写入方式的变迁

| 容量(目标)   | 典型的写人方式      | 写人时间的目标   |

|----------|--------------|-----------|

| ~64K     | 50ms 固定脉冲方式  | 64K/7min  |

| 64K~512K | 1ms 快速写入方式   | 512K/4min |

| 256K~1M  | 0.2ms 快速写入方式 | 1M/1min   |

| 1M~4M    | 0.2ms 快速翻页方式 | 1M/30s    |

| 4M~      | 50μs 快速翻页方式  | 4M/30s    |

## ●1.6.2 AM27C010 的编程方法

我们列举的Am27C010是AMD公司的UV EPROM。AMD公司UV—EPROM的高速写入方式称为"Flashrite Algorithm"。这种方式是在VPP端加上 12.75、Vcc端加上 6.75V的电压,在赋予 100 μ s脉冲状写入信号的同时,进行写入操作。

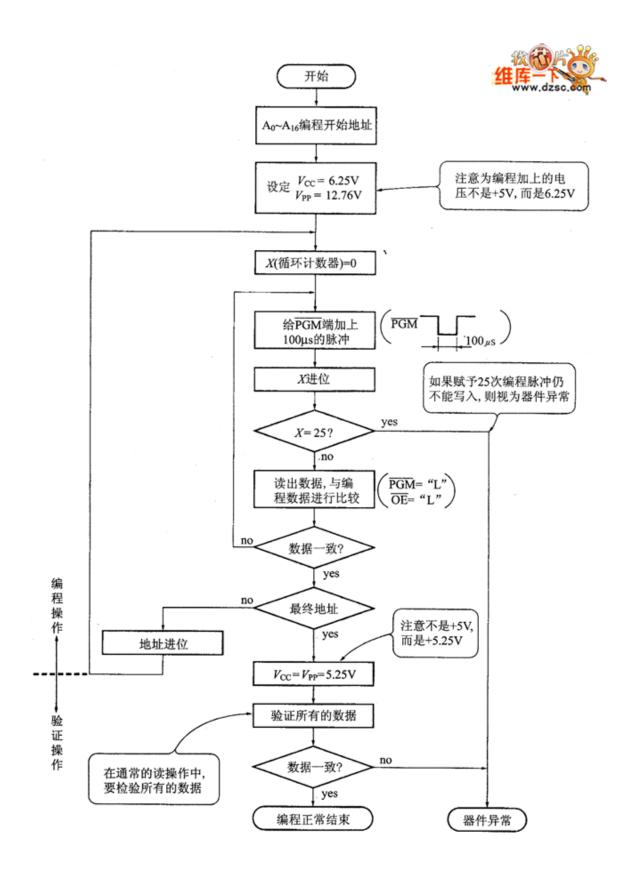

图 1 表示了写人算法。在如图所示的流程图中,在验证之前进行了 25 次的判断,这是 AMD 公司正式资料的原型。一般都认为判断是在编程验证之后进行的。在此的资料,记录了 AMD 正式的操作流程。

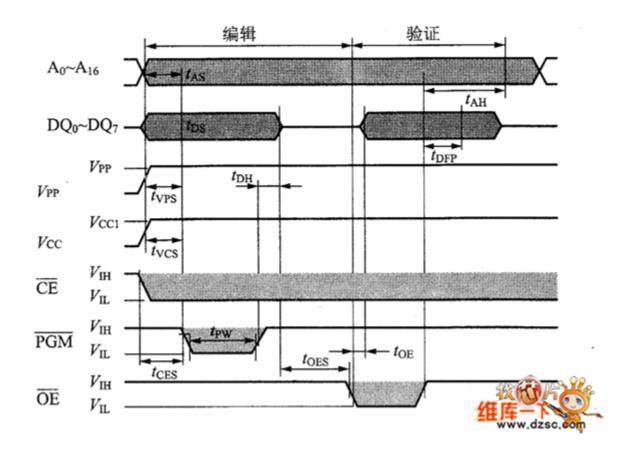

具体的操作波形如图 2 所示,各种时序规定如表所示。由于电源电压是用于编程的,所以除了出现VCC及VPP电压建立时间以外,波形自身与通常SRAM等的读/写操作等没有变化。但是观察表的单位就可以明白,地址建立等所必要的时间相当于 μ S数量级等,所以必须注意建立以及保持时间。

表 UV-EPROM 的写入时序

| 符 号<br>JEDEC 表示 一般表示 |                    | <b>.</b>             | E   | 时 序 |    |  |  |  |

|----------------------|--------------------|----------------------|-----|-----|----|--|--|--|

|                      |                    | 内 容                  | min | max | 单位 |  |  |  |

| $t_{ m AVEL}$        | $t_{ m AS}$        | 地址建立时间               | 2   |     | μs |  |  |  |

| $t_{ m DZGL}$        | toes               | OE建立时间               | 2   |     | μs |  |  |  |

| $t_{ m DVEL}$        | $t_{ m DS}$        | 数据建立时间               | 2   |     | μs |  |  |  |

| $t_{ m GHAX}$        | $t_{\mathrm{AH}}$  | 地址保持时间               | 0   |     | μs |  |  |  |

| $t_{\mathrm{EHDX}}$  | $t_{ m DH}$        | 数据保持时间               | 2   |     | μs |  |  |  |

| $t_{ m GHQZ}$        | $t_{ m DFP}$       | 从输出使能到输出高阻态          | 0   | 130 | ns |  |  |  |

| $t_{ m VPS}$         | $t_{ m VPS}$       | V <sub>PP</sub> 建立时间 | 2   |     | μs |  |  |  |

| $t_{\rm ELEH1}$      | $t_{\mathrm{PW}}$  | PGM编程脉冲宽度            | 95  | 105 | μs |  |  |  |

| $t_{ m VCS}$         | tvcs               | $V_{ m cc}$ 建立时间     | 2   |     | μs |  |  |  |

| $t_{\mathrm{ELPL}}$  | $t_{\mathrm{CES}}$ | CE建立时间               | 2   | -   | μs |  |  |  |

| $t_{ m GLQV}$        | $t_{\mathrm{OE}}$  | 由OE的数据制定时间           |     | 150 | ns |  |  |  |

图 1 Am27C010的编程流程

图 2 编程波形

#### ▲ 编程电压的添加

为 EPROM 提供编程电压。请注意:不但只给 VPP 提供 12.75V 的电压,还必须为 VCC 提供高于平时操作时电压的 6.25V 电压。在普通的写入装置中一般都搭载稳压器,但也需要考虑在写入过程中对于负载变化的响应。

#### ▲ 写入开始地址/数据配置

进行写人操作的地址和写人的数据需要分别配置给各地址总线和数据总线。UV-EPROM 可以针对任意地址进行写人操作。

地址、数据的信号线电平为普通的 TTL 电平。

#### ▲ 添加写脉冲

将 PGM 端设置为只有 100 μ s 的低电平。据此,向写人了"0"的 EPROM 内部存储器单元的浮置栅中注人电荷。

#### ▲ 编程验证

如果为/PGM 端提供写脉冲,则将在浮置栅处注入某种电荷。但并不能确认已经存储了使存储器单元确实只为"0"状态的足够的电荷。为此需要进行编程验证。编程验证中其他端口的状态以及电压保持不变,通过使/OE 有效来进行验证。

如果此时读出的数据一致,则表示写人操作完成,如果需要向下一个地址写入,则返回到步骤 2。

如果读出的数据不一致,则表明在先前的脉冲中电荷并没有被完全注人,因此返回步骤 3。但对同一地址的脉冲添加最多只能进行 25 次,如果提供了 25 次脉冲仍没有顺利写入,则表明该器件存在异常,以出错结束操作。

#### ▲ 读验证

在希望写入的范围中所有数据被正常写入后,将进行普通操作状态下的读操作,确认数据能否被正常读出。此时, Vcc 及 VPP 设置为 5.25V(普通操作的上限电压)。

如果写入的所有数据都能够被正常读出,则结束操作;如果数据不一致,则作为器件异常以出错结束操作。

## ●1.6.3 UV - EPROM 擦除器的制作

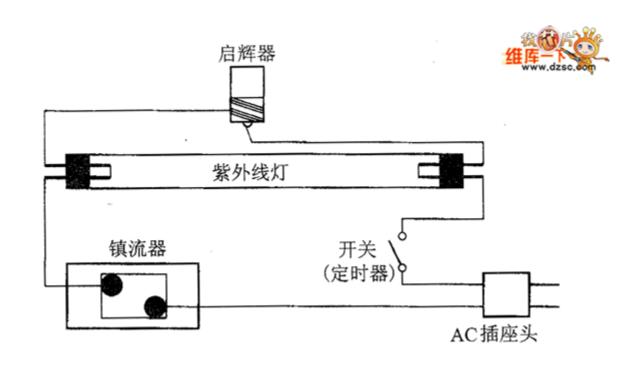

UV-EPROM的擦除操作是通过紫外线进行的。市场上虽然也有擦除器销售,但利用市场上销售的紫外线灯(杀菌灯)可以自己制作擦除器。制作非常简单,笔者曾经尝试着制作了一个。

#### 1. EPROM擦除器的电路

图是笔者尝试制作时使用的EPROM擦除器电路,这比真正的电路图简明易懂,是以与实际配线图近似的形式描绘的。紫外线灯也与荧光灯一样具有各种不同的大小和瓦数。如果是个人使用的擦除器,则选择较小的紫外线灯即可。我选择了4W的紫外线灯。另外,镇流器、启辉器的选择也要与紫外线灯相匹配。

图 UV-EPROM 擦除器电路

外壳使用铝盒等现成的盒子即可,只是要注意外壳在擦除过程中能保证紫外线不会直接射人眼中。

正如图中所示,紫外线灯的设置与普通的荧光灯相同。最近,市场上销售较多的是利用转换器缩短从打开开关到点灯这段时间的元器件。但EPROM擦除器不需要那样的功能,所以只利用非常简单的镇流器及启辉器制作即可。

如果为了缩短擦除时间,则应该在开关部位添加定时器等。但业余的可以利用厨房的定时器等, 经过一定时间后手工切断开关,这样就可以非常简单地完成制作了。

## 第二章

## 闪速存储器的结构与使用方法

## 2.1 闪速存储器的概要

闪速存储器的基本存储器单元结构如图 1 所示。一眼看上去就是n沟道的MOSFET那样的东西,但 又与普通的FET不同,特点是在栅极(控制栅)与漏极 / 源极之间存在浮置栅,闪速存储器利用该浮置 栅存储记忆。

图 1 闪速存储器的单元结构

浮置栅被设计成可以存储电荷的构造,栅极及主板利用氧化膜进行了绝缘处理,一次积累的电荷可以长时间(10年以上)保持。当然,如果氧化膜存在缺陷,或者由于某种原因使绝缘膜遭到破坏,那么闪速存储器将失去记忆。同时,因为热能必定致使电荷以某概率发生消减,因此数据保存的时间将受到温度的影响。

下面,我们将进一步讨论闪速存储器的擦除与写人的原理。

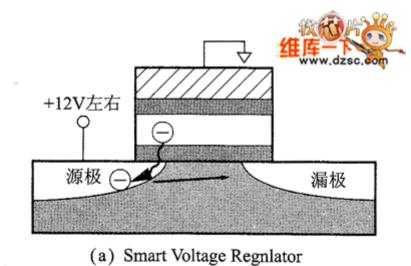

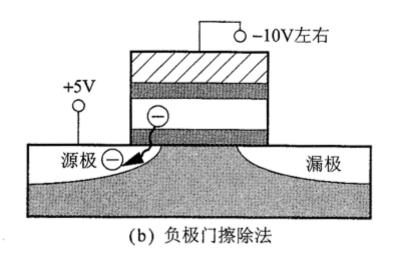

我们知道,数据的写人与擦除是通过主板与控制栅之间电荷的注人与释放来进行的。例如,一般的NOR闪速存储器在写人时提高控制栅的电压,向浮置栅注人电荷(图 2)。而数据的擦除可以通过两

种方法进行。一种方法是通过给源极加上+12V左右的高电压,释放浮置栅中的电荷(Smart Voltage Regulator);另一种方法是通过给控制栅加上负电压(-10V左右),挤出浮置栅中的电荷(负极门擦 除法)。各种电压提供方式如图 3 所示。

图 2 闪速存储器的写入操作

图 3 闪速存储器的擦除操作

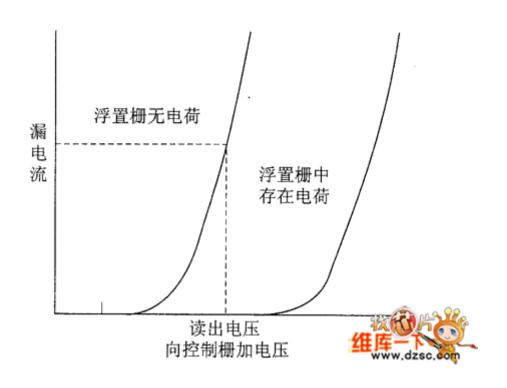

图 4 图示了闪速存储器单元的电压一电流特性。浮置栅的电荷可抵消提供给控制栅的电压。也就 是说,如果浮置栅中积累了电荷,则阈值电压(V<sub>th</sub>)增高。与浮置栅中没有电荷时的情况相比,如果 不给控制栅提供高电压,则漏极一源极间不会处于导通的状态。因此,这是判断浮栅中是否积累了电 荷,也就是判断是"1"还是"0"的机制。

图 4 闪速存储器单元的电压一电流特性变化

那么,写入操作是提高了 $V_{th}$ 还是降低了 $V_{th}$ 呢?根据闪速存储器的类型情况也有所不同。作为传统 EPROM的一般替代晶的NOR以及硅盘中应用的NAND闪速存储器,在写入时为高 $V_{th}$ ; 而AND及DINOR闪速存储器中,在写人时为低 $V_{th}$ 。

## 2.2 闪速存储器的分类及特征

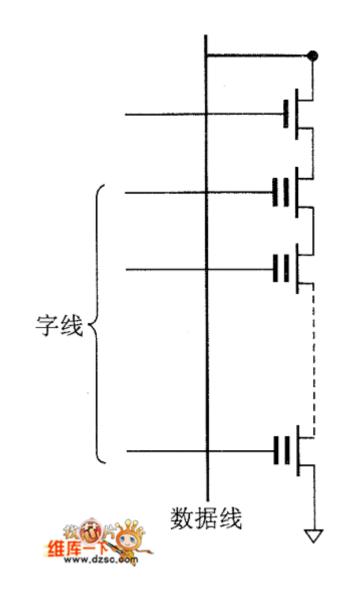

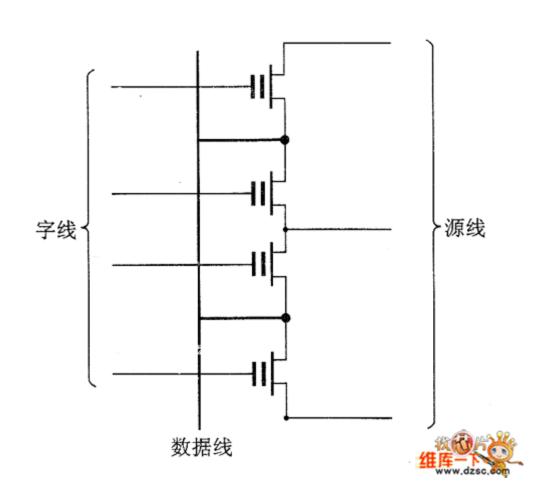

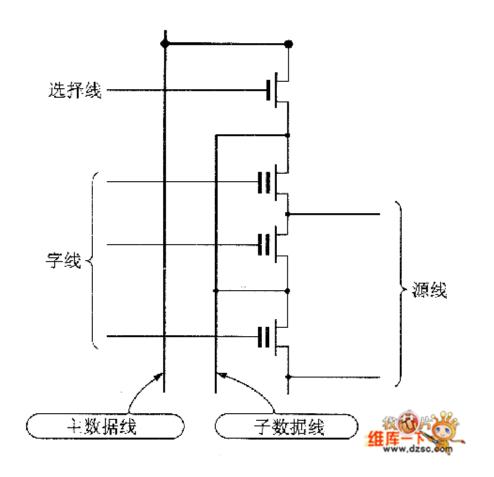

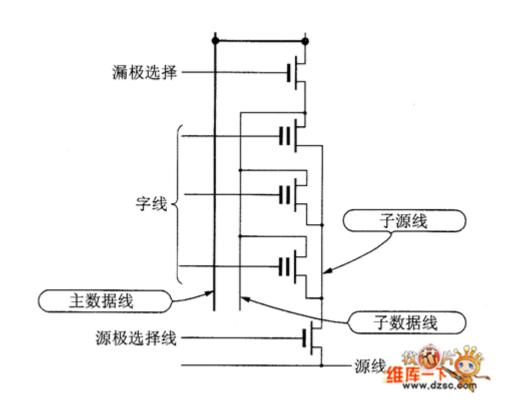

闪速存储器根据单元的连接方式,如表所示,可分成NAND、NOR、DINOR(Divided bit Line NOR)及AND几类。NAND闪速存储器单元的连接方式如图 1 所示,NOR闪速存储器如图 2 所示,DINOR闪速存储器如图 3 所示,AND闪速存储器单元的结构如图 4 所示。市场上销售的闪速存储器基本上就是NOR及NAND两种,其中只有NAND闪速存储器的单元是串联的,其他所有类型的单元都是并联的。

表 闪速存储器的单元方式

| 种 类   | 单元的连接方式     | 逻辑                    | 写人方法  | 擦除方法 | 数据存取 |

|-------|-------------|-----------------------|-------|------|------|

| NAND  | 串联          | 写入时为高 V <sub>th</sub> | 隧道注入  | 隧道释放 | 顺序存取 |

| NOR   | 并联          | 写入时为高 $V_{\rm th}$    | 热电子注入 | 隧道释放 | 随机存取 |

| DINOR | 并联(数据线分层)   | 写入时为低 V <sub>th</sub> | 隧道注入  | 隧道释放 | 随机存取 |

| AND   | 并联(数据/源线分层) | 写人时为低 V <sub>th</sub> | 隧道注人  | 隧道释放 | 顺序存取 |

NOR闪速存储器以读取速度 100ns的高速在随机存取中受到人们的青睐。但由于其单元尺寸大于 NAND闪速存储器,存在着难以进行高度集成的问题。写人时采用CHE (Channel HotElectron,沟道热电 子)方式,即在栅一漏之间加上高电压,提高通过沟道的电子能量,向浮置栅中注入电荷。这样,由于损耗电流变大,在写入时必须由外部其他途径提供+12V左右的电源,因而不适合低电压操作。

图 1 NAND 闪速存储器的单元结构

图 2 NOR 闪速存储器的单元结构

与 NOR 闪速存储器相比较,东芝公司开发的 NAND 闪速存储器却能够进行高度集成,写人方式也因 采用了被称为隧道的方式,即利用了氧化膜所引起的隧道效应现象,故与 NOR 闪速存储器相比,具有 损耗电流较小的特征。但在另一方面,由于单元是串联连结的,所以面向顺序存取,具有随机存取速 度慢的缺点。

图 3 DINOR 闪速存储器的单元结构

三菱与日立结合NAND及NOR闪速存储器的特点,开发了DINOR(Divided bit—line NOR)闪速存储器以及AND闪速存储器。

DINOR闪速存储器的结构是将数据线(位线)分离成主数据线与子数据线的层次,通过各个存储器单元与子数据线的连接,既可以具有像NAND那样的高度可集成性,又具各与NOR同等程度以上的高速随机存取性。因为写人操作也采用了隧道方式,所以较小的写入电流就可完成写人操作。又因数据置换所需要的高电压升压电路可以设计于芯片内部,因此可以进行低电压的单一电源操作。

图 4 AND 闪速存储器的单元结构

AND闪速存储器单元的源线也设计了分离的子源线,是倾向于顺序存取的产品。除了能够以与硬盘一个扇区相同的 512 字节大小的小块单位进行写人及读取操作以外,还具有DINOR的低功耗特长,可以面向硅盘等展开应用。单元的连接方式与NOR闪速存储器相同,写入逻辑为反相(NOR写人时V<sub>th</sub>变高,而AND式则降低),命名为AND式。

现在的NOR闪速存储器也致力于改良,目的在于将写人操作也采用隧道方式以降低功耗,或者通过单元物理结构上的改善等,使低电压单一电源类型的闪速存储器也形成产品。以文件为使用目的的AND及NAND两种类型的闪速存储器目前已在市场上流通,应用于大容量的Flash ATA卡等方面。

## 2. 3 NAND 闪速存储器

## ● 2.3.1 TC58V64 的引脚配置

TC58V64的引脚配置如图所示。在图中未看到地址引脚,这是因为利用数据输入输出引脚(I/0<sub>1</sub>~I/0<sub>8</sub>),能够以时分方式赋予数据。NAND闪速存储器只能以基本的块单位进行顺序存取,所以不需要以随机存取为前提的地址引脚。

图 TC58V64AFT的引脚配置

接着我们针对各个信号引脚进行简单的说明。

#### $\blacktriangle$ I / $0_1 \sim I$ / $0_8$

这样的信号引脚进行着地址、指令及数据的输入输出等,与ALE及CLE信号等配合,以时分方式复用。

▲ /CE (Chip Enable, 芯片使能)

这是器件的选择信号。电平为低电平时,器件处于选择状态;为高电平时,器件处于非选择状态(低功耗状态)。

▲ /WE (Write Enable, 写使能)

将I/0端置于输入(由主机向器件赋予数据等)状态。

▲ /RE (Read Enable, 读使能)

这是用于使I/0引脚进行数据输出的信号。/RE也作为内部地址计数器进位的时钟来工作。

RE有效(为低电平),经过存取时间(tREA)后,I/0引脚上的数据得到确定,在/RE的上升阶段,内部地址计数器只向前移动一位。这样,单一的读操作就可以读出连续地址的存储器内容。

▲ CLE (Command Latch Enable, 指令锁存使能)

这是向器件内部的指令寄存器中写人给予 I / 0 引脚的操作指令码的控制引脚。在/WE 信号上升与下降时,如果 CLE 有效(为高电平),则作为指令将被锁存。

▲ ALE (Address Latch Enable, 地址锁存使能)

这是判断主机给予 I/0 引脚的数据是地址还是数据的信号。ALE 如果有效(高电平),则作为地址来处理; ALE 如果无效(低电平),则作为数据进行处理。

#### ▲ /WP (Write Protect, 写保护)

强制禁止进行写人及擦除操作。如果/WP 有效(低电平),则芯片内部的升压电路被复位。由于 存储器单元不能生成用于写人的高电压,所以即使发出了指令,替换操作也不能被执行。

在上电、断电以及容易使操作不稳定的情况下,使该引脚持续有效,则系统处于安全状态。

#### ▲ R/B (Ready/Busy,就绪/忙输出)

这是用于向外部通知器件内部操作状态的信号,是漏极开路输出。如果内部正在进行操作,则该信号有效(为低电平),如果内部操作完成,则该信号无效(为高电平)。

这些控制信号的组合与工作状态的关系如表所示。

表 TC58V64的操作

| 操作模式       | 控制信号线(X:无影响) |     |    |          |          |    |  |  |  |

|------------|--------------|-----|----|----------|----------|----|--|--|--|

| 探作领以       | CLE          | ALE | ĈĒ | WE       | RE       | WP |  |  |  |

| 指令输入       | Н            | L   | L  | <b>†</b> | L        | Х  |  |  |  |

| 数据输入       | L            | L   | L  | <b>†</b> | Н        | X  |  |  |  |

| 地址输入       | L            | Н   | L  | <b>†</b> | Н        | X  |  |  |  |

| 串行数据输出     | L            | L   | L  | Н        | <b>\</b> | X  |  |  |  |

| 编程期间(Busy) | X            | X   | X  | Х        | X        | Н  |  |  |  |

| 擦除期间(Busy) | X            | X   | X  | Х        | Х        | Н  |  |  |  |

| 编程擦除禁止     | X            | X   | X  | X        | X        | L  |  |  |  |

## ● 2.3.2 NAND 闪速存储器的内部结构

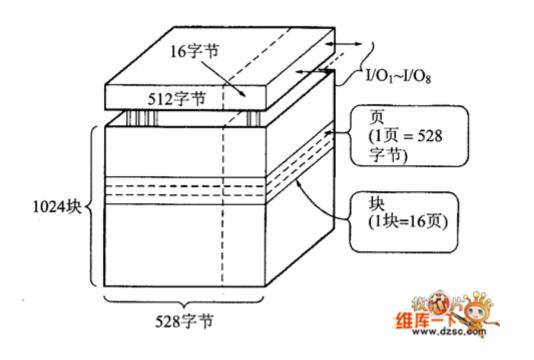

TC58V64的内部结构如图所示。闪速存储器的容量增大,则块数也将增加,但内部的基本结构没有改变。

图 TC58V64 的内部结构

NAND 闪速存储器的特点

- ①按顺序存取数据;

- ②存储器内部以块为单元进行分割,而各块又以页为单位进行分割;

- ③以块为单位进行擦除操作:

- ④以页为单位进行编程(写人);

- ⑤页的大小存在尾数(TC28V64 是 528 字节);

- ⑥也存在有坏块(bad block)的产品。

以NAND闪速存储器为主的用途是类似硅盘那样的文件保存器件。所谓的 528 写入页大小,就是在 512 字节(相当于一般的硬盘扇区大小)上增加了 16 字节的冗余数据字节,通过在这些冗余字节上 添加纠错码,在写人与擦除的重复操作中,即使闪速存储器单元发生异常,数据也可以复原。

另外,作为擦除的单位,即一块 16 页(转变为数据大小就是 512 字节×16=8K)最好与主机端的文件管理单位一致。

当读者看到特点⑥,即和普通存储器器件特点相同的最后一条,应该稍微有些吃惊吧。在产品供货期间,所有数据未成为FFH的块都作为坏块不进行擦除操作,必须做到在主机的文件管理软件中不利用这些坏块。TC58V62最多容许有10个坏块,由于TC58V64具有1024个块,所以它有时只能利用1014个块。

## ● 2.3.3 操作指令

TC58V64的操作指令(通过指令输人所给予的编码)如表所示。只有自动块擦除是2字节指令,其他都是1字节指令。

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 数据   | 指令   | 指令     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------|

| 备注                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 第二周期 | 第一周期 |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 80h  | 串行数据输入 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 00h  | 读模式(1) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 01h  | 读模式(2) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 50h  | 读模式(3) |

| Busy 信号有效时可发布                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | FFh  | 复位     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 10h  | 自动编程   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D0h  | 60h  | 自动块擦除  |

| Busy 信号有效时可发布                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | 70h  | 状态读    |

| A CONTRACTOR OF THE PARTY OF TH |      | 90h  | ID读    |

表 TC58V64的操作指令

下面我们就针对这些指令与存取操作进行说明。

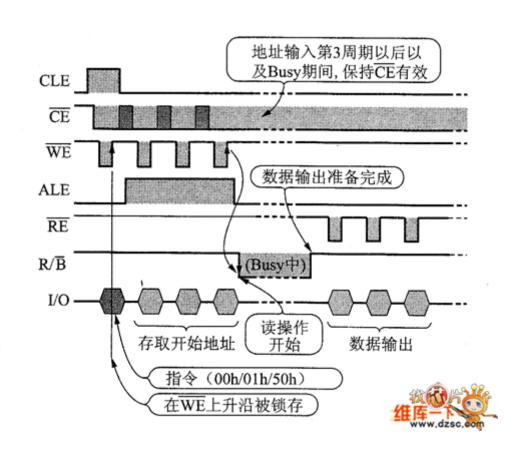

## ▲数据读操作

TC58V64的读操作如图 1 所示。随着指令,利用 3 个字节指定读出开始地址,开始进行数据读操作,地址及指令在WE信号的上升沿被锁存。

图 1 TC58V64 的读操作

读操作时地址的指定方法如表 1 所示。最先给予的数据称为列地址,后面的两个周期中所给予的数据称为页地址。TC58V64 的存储器具有1024个块,由于各个块又分割成 16 个页,所以A22~A13 为块号(块地址),A12~A19 为块内的页号(块内的NAND地址)。

表 1 指定地址的方法

| 地址周期 | 1/0引脚            |                   |                  |                 |                 |                 |                  |                  |  |  |

|------|------------------|-------------------|------------------|-----------------|-----------------|-----------------|------------------|------------------|--|--|

|      | I/O <sub>8</sub> | I/O <sub>7</sub>  | I/O <sub>6</sub> | I/Os            | 1/04            | 1/03            | I/O <sub>2</sub> | I/O <sub>1</sub> |  |  |

| 第一周期 | A <sub>7</sub>   | . A <sub>6</sub>  | A <sub>5</sub>   | A <sub>4</sub>  | A <sub>3</sub>  | $A_2$           | $A_1$            | A <sub>0</sub>   |  |  |

| 第二周期 | A <sub>16</sub>  | A <sub>15</sub> . | A <sub>14</sub>  | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub>  | A <sub>9</sub>   |  |  |

| 第三周期 | "0"              | "0"               | A <sub>22</sub>  | A <sub>21</sub> | A <sub>20</sub> | A <sub>19</sub> | A <sub>18</sub>  | A <sub>17</sub>  |  |  |

读指令如果是 00h, 则 A8 = "0", 如果读指令为 01h, 则 A8 = "1", 所以没有指定 A8 的位。

A22~A13: 块地址

A12~A9: 块内 NAND 地址

A7~A0: 列地址

这里有意思的是 A8 没有指定,而 1 页的大小为 528 字节,大于 512。这样 A9 就成为了页地址。

在此,将一页(528字节)分成256+256+16这样的结构(假设称为段)可能更容易理解。根据从一页的哪个段开始读,指令将被分离,读指令具有3个种类(00h,01h,50h)正是因为这个原因。而从各个段中的什么部位开始读是由列地址过渡的。当然,在最后的16字节的地方,列地址只能取得0~15的值。

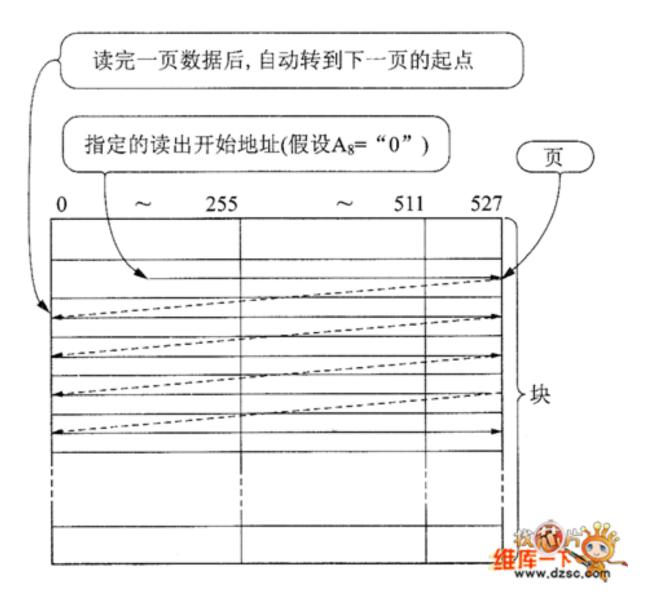

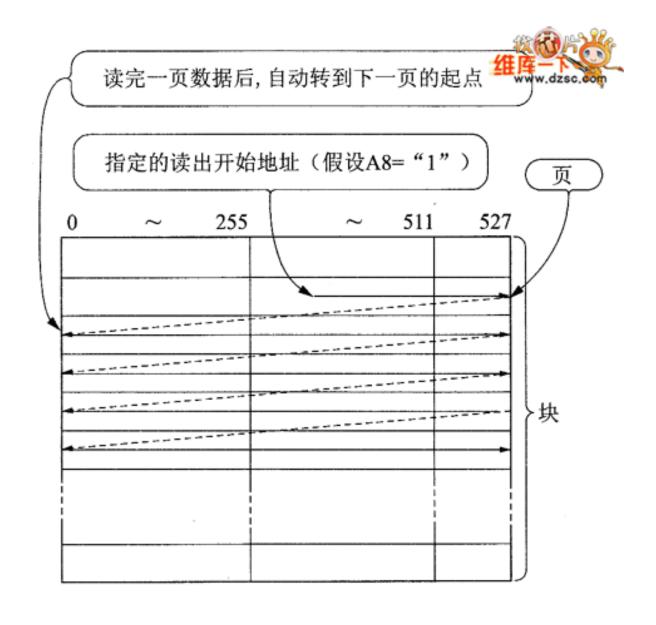

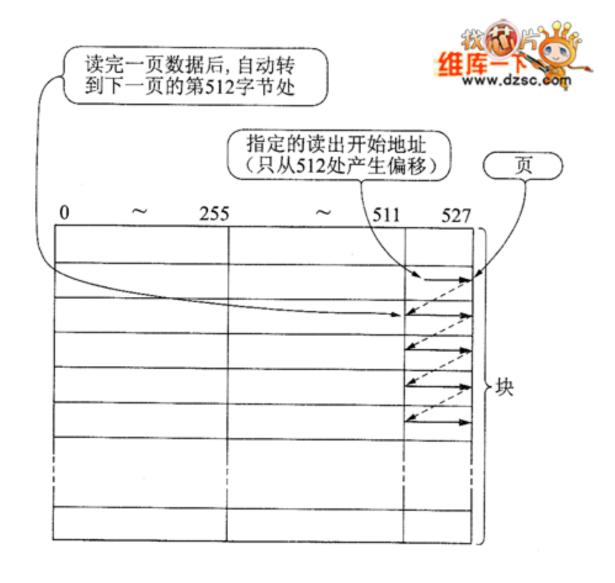

在指令代码为 00h, 01h 的情况下,将从读取开始地址到一页的最后地址传输数据,一旦到达最终的地址,则输出下一页的起始数据。仅当指令代码为 50h[读指令(3)]的时候,如果到达页的最后部分,则由下一页的第 512 个字节(第 3 部分)开始输出,而不返回到页的起始。

这些操作模式如图 2、图 3、图 4 所示。

图 2 顺序读(1)

图 3 顺序读(2)

图 4 顺序读(3)

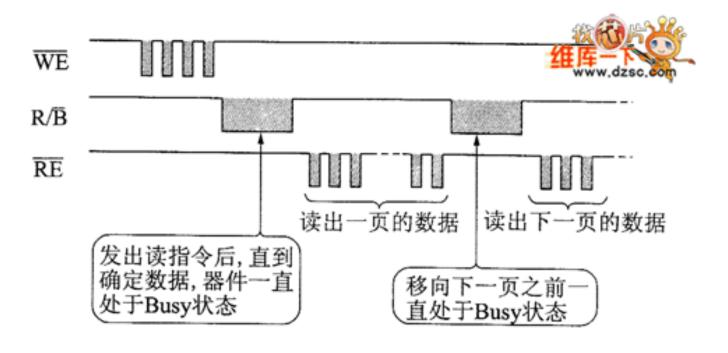

如图 5 所示,当进行读操作时,在指定地址后到读取最初数据之间以及到达页的结尾部位后。需要一定的时间返回到下一页的起始部分(顺序读(3)的情况下为第 3 部分的起始)。这期间Busy信号有效,需要让来自主机的访问等待。这段时间可以认为是内部一页的数据(528字节)传输到页缓冲器上的时间。

图 5 读操作中的 Busy 状态

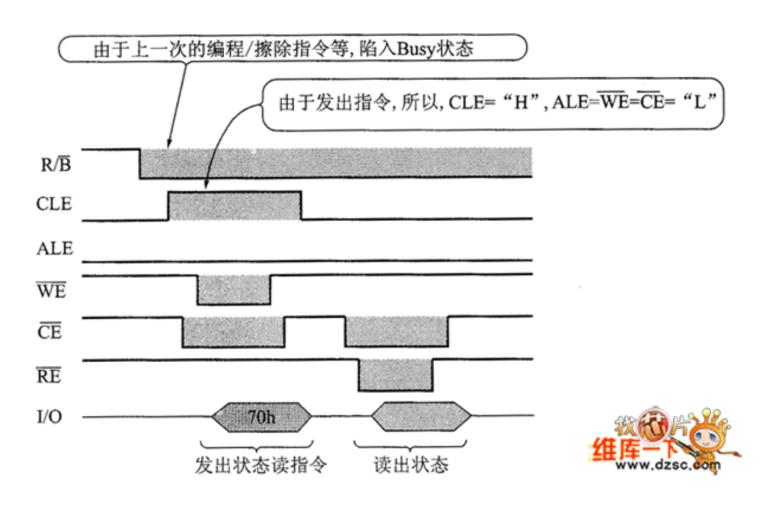

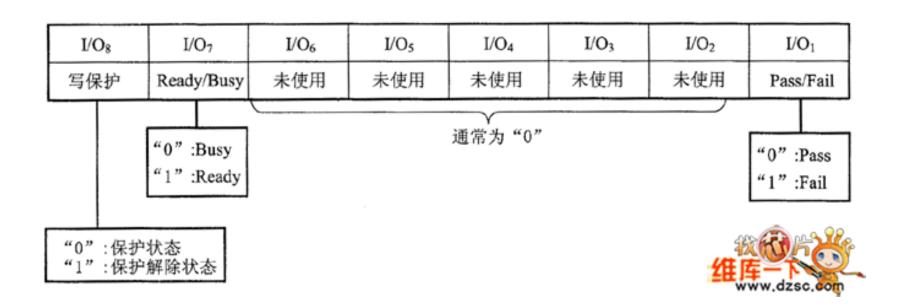

## ▲状态读

状态读的操作如图 1 所示,如果跟着指令 70h进行读取操作,则读出存储器的状态。存储器的状态数据如图 2 所示。

图 1 状态读操作

图 2 TC58V64 的状态

## ▲自动页编程操作

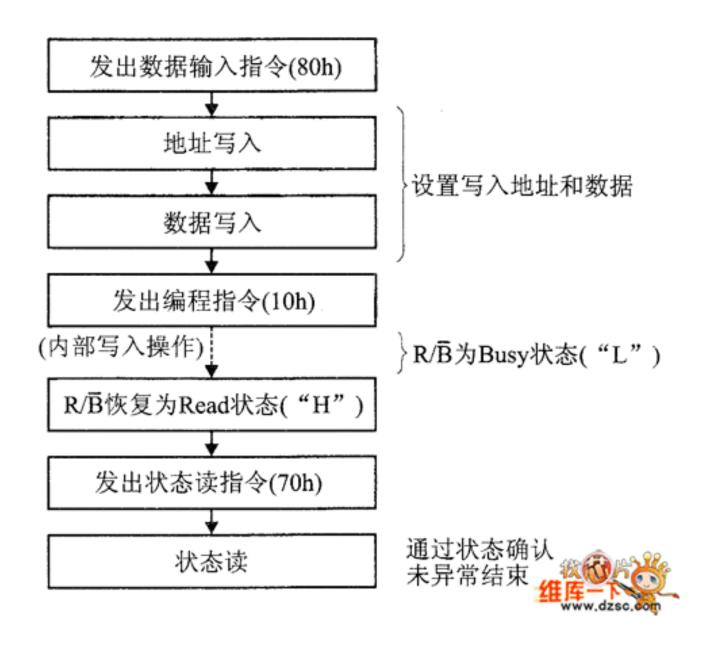

自动页编程操作按照如下的程序进行:

- ①发出数据输入指令(80h);

- ②地址/数据输入;

- ③发出自动编程指令(10h)。

图对上述流程进行了图示。在器件的内部工作中,在②中所给予的数据不是直接写人存储器中的,而是先暂时存人页缓冲器中。通过③开始送出写入指令,然后转发到②所提供的页地址处。

图 自动页编程的操作流程

此时,在芯片内部进行写人验证。如果正常,则恢复R/B设置为Ready状态(为高电平)后正常结束。如果由于某些异常导致写人验证未正常进行的,则在内部自动进行重试,如果重试达到所规定的次数,则将R/B设置为Ready状态的同时结束异常。

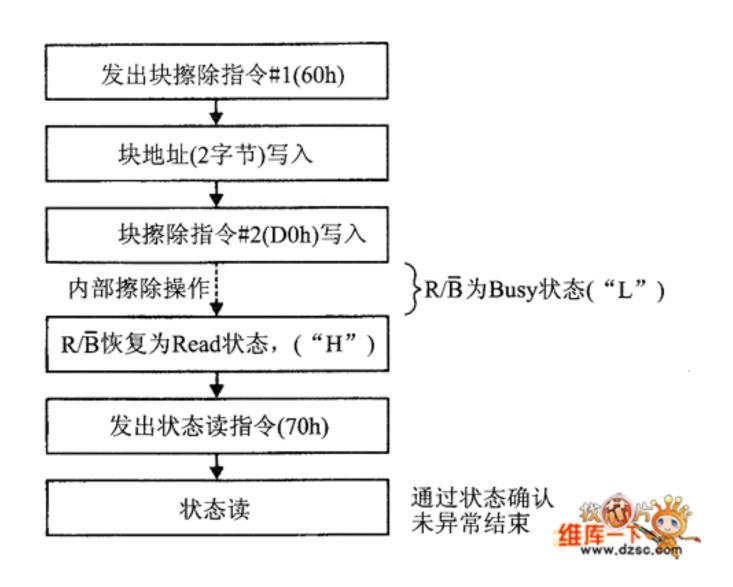

## ▲自动块擦除

自动块擦除是将指定的块的内容一次性设为 FFh。正如先前所描述的那样,虽然写人操作是以页 (528 字节) 为单位进行的,但擦除只能以块为单位进行。由于块擦除所提供的地址是块地址,所以 占有 2 个字节。

自动块擦除的工作流程如图所示。与自动页编程的操作相同,在内部也进行自动重试,如果重试规定次数以后仍然存在异常,则将 R / B 设置为 Ready 状态的同时结束异常。

图 自动块擦除的操作流程

## ▲复位操作

复位操作通过指令代码FFh的写人来进行。一旦发出该指令,内部用于编程/擦除的升压电路将断开,编程/擦除电压放电直至电压为0V。在放电这段时间内,R/B信号维持为Busy状态(低电平)。

利用复位指令,地址寄存器的各个位全部为"0",数据寄存器中的位都为"1"。

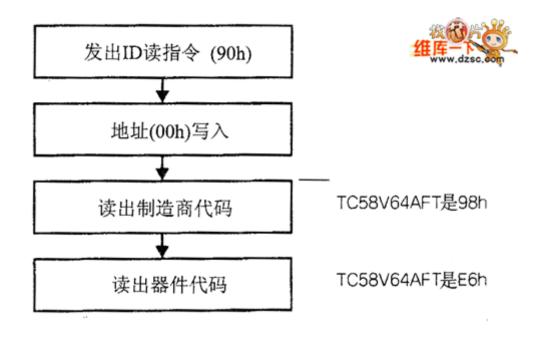

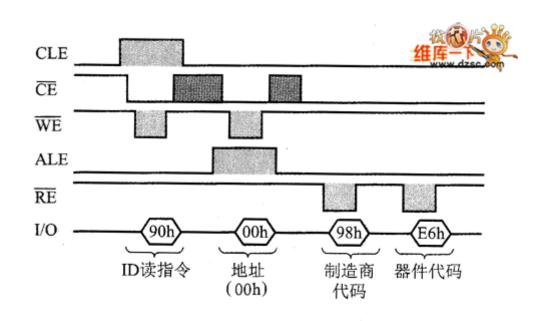

## ▲ID 读操作

ID代码是为了主机自动识别与总线连接的器件的制造商名称/器件型号而设置的。ID读指令用于读取该ID代码。

图 1 图示了ID读操作的流程。图 2 图示了发送ID读指令的操作。

图 1 ID 读指令的躁作流程

图 2 ID 读指令的操作

在读取ID时,发送ID读指令(90h)之后,写人00h作为地址。由于90h是指令,所以虽然将CLE设为有效(高电平),但由于紧跟着的00h是地址值,所以CLE无效(低电平),而ALE有效(高电平)。

完成这样的流程后,通过下面 2 次的读取,可以读出制造商代码(TC58V64为 98h)和器件代码(TC58V64 为E6h)。

# 2. 4 NOR 闪速存储器

# ● 2.4.1 引脚配置

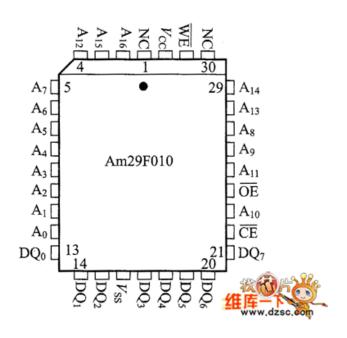

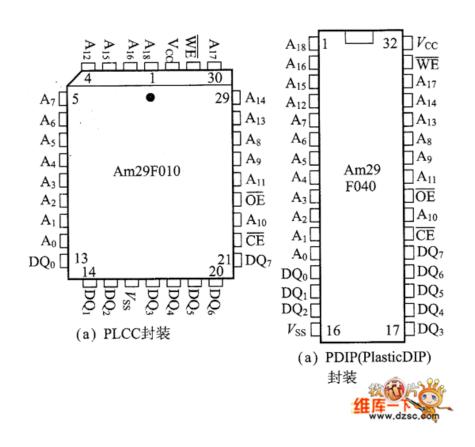

在器件的使用方面,必须了解引脚配置以及各个引脚所代表的意思,因此我们现在首先调查引脚的配置。下载Am29F010A的数据手册后,没有关于DIP封装的记载。但是,因为事实上Am29F010的DIP类型是存在的,所以引脚配置肯定已经确定了。我们试着与相同系列的前一产品Am29F040B的引脚配置进行比较。Am29F010A的PLCC式的引脚配置如图 1 所示,Am29F040B的PLCC式与DIP式的引脚配置如图 2 所示(Am29F010A与 040B除此之外都还有TTSOP式的封装)。

图 1 Am29F010 的引脚配置 (PLCC 封装)

将 Am29F010 与 Am29F040B 所具有的 PLCC 式的引脚配置进行比较,我们可以知道,前者中为 NC(Not -Connected, 无连接)的引脚 6 与 9 只是配置了地址的 2 个高位(A17 和 A18)。

图 2 Am29F040 的引脚配置

因此,对于Am29F010A的DIP式的引脚配置,也可以认为只是将Am29F040B的DIP式的引脚 30 和引脚 1 作为NC来使用。

目前我们都是在研究封装器件的内部结构,封装的外形虽然存在各种各样的形式,但取出其中芯片的管芯(die)则是完全一样的。管芯周围填充了为引出信号而布置的垫片,由垫片引出细电线(接合线)与封装的引脚相连接,由于不会有人故意将引线交叉设置,所以信号按序排列的管芯即使封装改变也不会有任何影响。

当然,接合线本身尽可能短,不但在成本方面,而且在特性方面也是有利的,所以封装中管芯的方向需要根据封装形式而加以改变。想象芯片中管芯以哪种方向进行配置以及如何布线是一件有意思的事情。

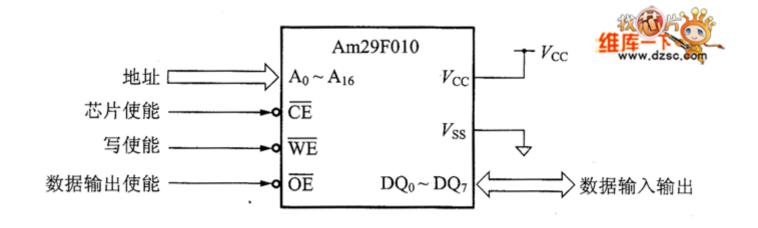

# ● 2.4.2 信号的种类

Am29F010引脚的分组如图所示。Am29F040只是地址总线增加到 18 根,没有NC引脚,其他方面与 Am29F010 完全相同。闪速存储器的操作与地址、数据、/CE、/OE、/WE的组合如表所示。

图 Am29F010 的引脚分组

| 操作   | $A_0 \sim A_{16}$ | CE                   | ŌĒ  | WE  | $DQ_0 \sim DQ_7$ |

|------|-------------------|----------------------|-----|-----|------------------|

| 读    | 地址输入              | "L"                  | "L" | "H" | 数据输出             |

| 写    | 地址输入              | "L"                  | "H" | "L" | 数据输入             |

| 待机   | X                 | $V_{\rm CC}\pm$ 0.5V | X   | X   | 高阻抗              |

| 输出禁止 | 输出禁止 X            |                      | "H" | "H" | 高阻抗              |

| 硬件复位 | X                 | X                    | X   | X   | 高阻抗              |

表 Am29F010A的操作模式

## ▲ VCC / Vss

这是电源引脚。因为Am29F010和Am29F040都是+5V单一电源工作的FlashROM,因此,给Vcc加上+5V电压,Vss作为标准电位为 0V。

### ▲ A0~A16 (地址)

$A0\sim A16$  是地址引脚。虽然 Am29F010 是容量为 1M 位的闪速存储器,但由于是以  $DQ0\sim DQ7$  的 8 位为单位进行数据输入输出,因此地址就是 1M 位÷8 位=128K,具有 17 根地址线。

## ▲ DQ0~DQ7(数据)

这是与外部进行数据传输的引脚。因为 Am29F010 通常是以 8 位为单位进行输入输出的, 所以数据通常是以 8 位为单位进行读取与写人的。

## ▲ /CE (芯片使能)

这是器件的选择信号。只有该引脚为低电平时,下面所描述的/OE及/WE信号才有效。当与CPU等连接时,对CPU的高位地址进行解码,然后输人到该引脚。

当存在多个器件时,通常是/CE以外的引脚全部并联,由/CE引脚确定访问那个器件。

## ▲ /OE (输出使能)

只有在上面所说明的/CE引脚为低电平时/OE才有效。从Flash ROM读出数据时,如果/OE与/CE都为低电平,则一定时间后DQO~DQ7引脚上将出现数据。因为没有表示收集有效数据的信号,所以在外围电路中,根据数据手册中的值,预测数据已被确定的时间,然后读出出现在DQO~DQ7中的数据。

### ▲ /WE (写使能)

该引脚只是在先前说明的/CE 引脚为低电平时才有效。在赋予闪速存储器指令及写人数据等时,该信号与/CE 引脚一起同为低电平。

事实上数据是在/CE 及/WE 信号的上升沿(由低电平上升为高电平的时候)被提取到芯片内部的。

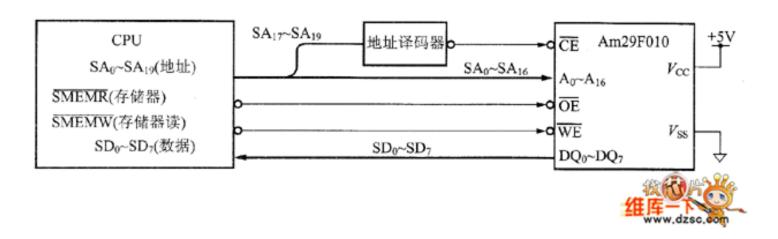

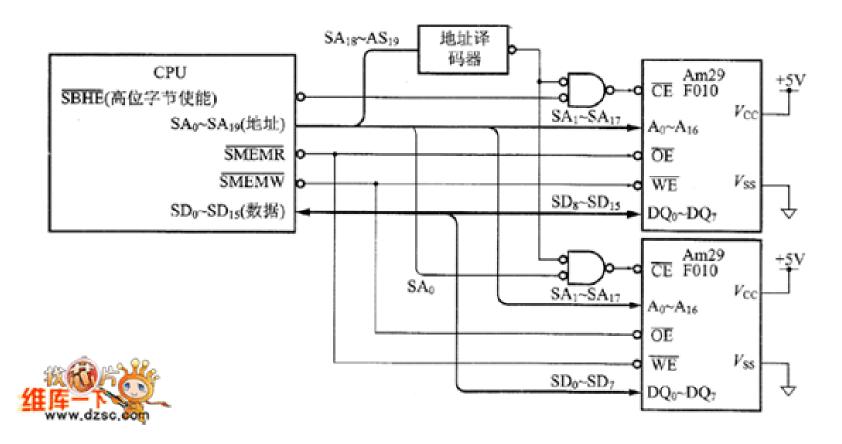

## ●2.4.3 与处理器的连接实例

表示闪速存储器与CPU的连接模式如图 1 所示。该图中信号名与信号的意思吻合ISA总线,通过地址译码器对CPU地址的高位进行解码,如果属于闪速存储器范围.则使/CE信号有效,将地址的低位赋予闪速存储器。

图 1 8 位 CPU 与闪速存储器的连接思路

进而/OE与SMEMR信号、/WE与SMEMW信号相连, DQo~DQz连接于CPU的数据总线。

该图中特意考虑到时序的关系。根据CPU的总线工作时间,或者需要仔细计算时间,或者使其等待、延长总线周期等。ISA总线与近期的闪速存储器工作等相比,其速度是足够缓慢的,所以该图可以在添加缓冲器的电路中工作。

如果CPU的数据总线超过 8 位(16 位或者 32 位宽等),则需要排列若干个闪速存储器。但是一般的CPU即使数据总线具有 16 位或者 32 位,作为命令一般设计时也是以 8 位为单位进行输入输出的。为了适应这样的命令,一般CPU的外部数据总线也以 8 位为单位进行分组,并且设计了在读写时标明存取所对应的分组信号。

以图 2 为例,表示在 16 位的CPU中连接了 2 个Am29F010 的电路。这里的信号种类与名称是以ISA总线为基准的(事实上在ISA上进行 16 位的存取需要使MLMCS16 有效,在此省略)。与前图相比,我们知道增加了SBHE信号,该信号用于表示是否使用数据总线的高 8 位,对低 8 位的访问是由A0 确定的。表总结了ISA总线上存取操作与A0、SBHE信号的操作。信号名存在若干不同,但处理器基本上都采用相同的方法。

图 2 16 位 CPU 与闪速存储器的连接思路

表 在16位总线上的存取操作实例

| M 4D HI 16-   | 信号             | 状态   | 数据有效/无效          |                                  |  |

|---------------|----------------|------|------------------|----------------------------------|--|

| 总线操作          | A <sub>0</sub> | SBHE | $SD_0 \sim SD_7$ | SD <sub>8</sub> ~SD <sub>1</sub> |  |

| 偶数地址的字节(8位)存取 | "L"            | "H"  | 有效               | 无效                               |  |

| 奇数地址的字节(8位)存取 | "H"            | "L"  | 无效               | 有效                               |  |

| 偶数地址的字(16位)存取 | "L"            | "L"  | 有效               | 有效                               |  |

注: 进行由奇数地址的字存取时, 是分割奇数地址与偶数地址的字节存取(2次存取)来运行的.

由此表我们知道,由于 A0 与低位字节的选择信号等价,所以地址偏移一个,将 A1~A17 赋予了闪速存储器。当地址一致、A0 为低电平时,低 8 位的闪速存储器的面有效;当 SBHE 为低电平时,高 8 位的闪速存储器的 CE 有效。

上述的例子为 16 位的 CPU。在 32 位以上 CPU 的情况下,没有 A0 及 A1,而是准备了以字节为单位的使能信号(大多命名为/BE0,/BE1,/BE2,/BE3 等名称)作为替代。

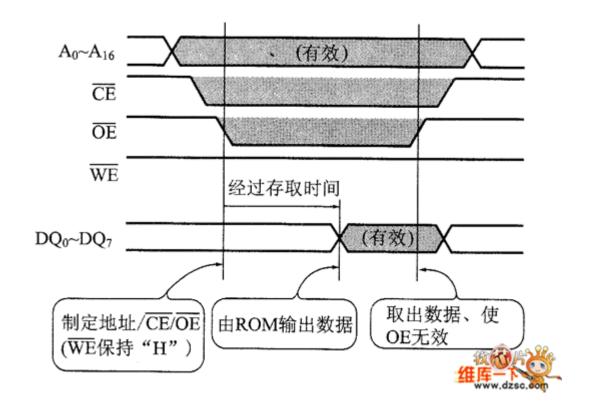

# ● 2.4.4 读周期的概要

下面我们来看看闪速存储器读周期的时序。基本的存取方法的思路如图所示。

图 闪速存储器的读操作

将希望访问的地址提供给 A0~A16, 一旦/CE、/OE 有效(低电平),则由闪速存储器开始读出数据(因为是读操作,所以/WE 保持高电平)。

数据在何时被确定是由地址./CE./OE 各自确定后的延迟时间(存取时间)规定的,是由最迟的时间确定数据的。

例如,Am29F010A-55 由地址及/CE 的存取时间为 55ns,由"/OE 的存取时间为 30ns。如果地址确定了的同时,/CE、/OE 同时有效,则 55ns 后将出现有效数据;在地址确定、CE 一直有效的稳定状态时,只要/OE 有效,则 30ns 后数据确定。

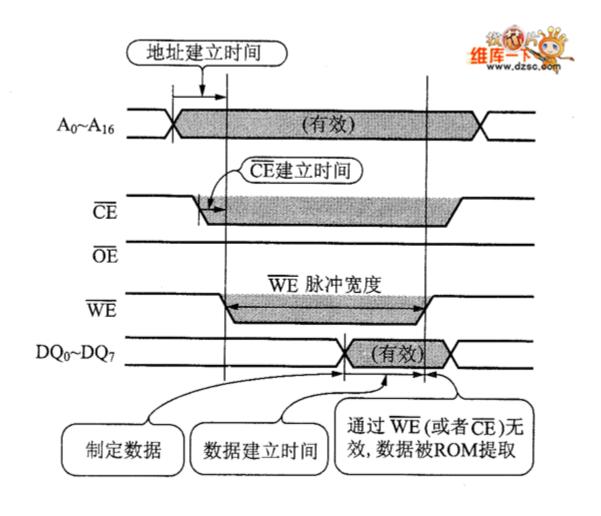

# ● 2.4.5 写周期的概要

写周期的基本思路如图所示。因为这次是写的方向,所以/OE 保持高电平,由主机方面赋予数据 (DQ0~DQ7)。

图 闪速存储器的写操作

当/WE 和/CE 双方都为低电平时,进行写操作的地址被提取到闪速存储器内部。而在/WE 和/CE 双方都变成低电平后,在任何一方上升为高电平阶段(由低电平到高电平的变化中),数据被提取到闪速存储器内部。通过/WE 进行的写操作称为/WE 写控制;通过/CE 进行的写操作称为/CE 写控制。一般情况下利用/WE 写控制的较多,所以图示的也是/WE 写控制的过程。

写操作时必须要注意的是地址及数据等各信号的建立时间。进行读操作时,只要等待地址、/CE、/OE 确定. 从目的地址中就可以发出数据,因此对于确定的顺序就没什么必要给予注意。但是在写操作的情况下,如果不考虑地址、数据以及控制信号的时序,将会发生写人到错误的地址中或者没有正确接收数据的情况。

需要特别注意的是建立时间。如图所示,既需要在/WE 下降之前确定/CE 及地址,又需要在/WE 上 升的一定时间之前确定数据。

详细的数值我们以后再进行说明。例如 Am29F010-55 的地址及/CE 的建立时间(分别为 tAs、tCS)最小都为 0。建立时间最小为 0 可能有些难以理解,解释为关键不能为负数可能比较容易理解。如果/CE 的建立时间为负,即/CE 是在以后成为低电平的,这样就变成了/CE 写控制。所以说,/WE 写控制的最小值为 0 是理所当然的。

数据在/WE 上升之前被确定, Am29F010-55 最小需要 20ns (tDS)。也就是说。在/WE 上升至少 20ns 之前, 数据就必须被确定。

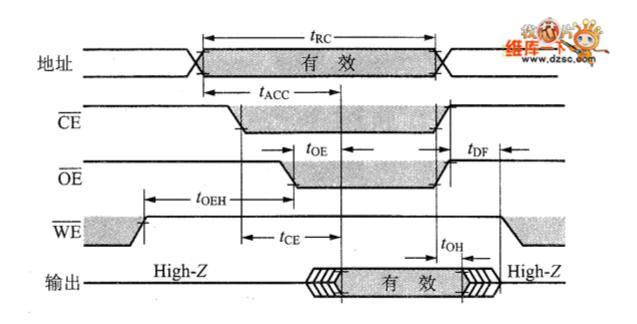

# ● 2.4.6 读周期的时序

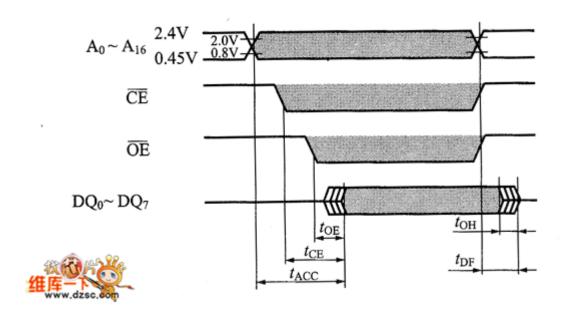

下面我们看一下数据手册中原有的、具体的读周期时序。图是Am29F010A的读操作的时序图,表是时序规定。与前所概述的内容相比较,在时序图当中,作为基点的电压存在两处,比概略图具有更多的时间规定。

图 Am29F010A 的读操作时序

|    | 1   | <u> </u>                    |   |

|----|-----|-----------------------------|---|

| 表  | п   | 序规                          | = |

| 7  | нл  | 1 <del>-1-&gt; 1-</del> 111 | 7 |

| AX | нт. | יונא יו ו                   | ᄮ |

|    |     |                             |   |

| 符号                  |                   | 45. W.                                                                | A 104                                                                         |     | 速度选项 |     |     |    |      |    |  |

|---------------------|-------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|------|-----|-----|----|------|----|--|

| JEDEC               | Std               | 参数                                                                    | 条 件                                                                           |     | -45  | -55 | -70 | 90 | -120 | 单位 |  |

| $t_{\mathrm{AVAV}}$ | $t_{ m RC}$       | Read Cycle Time                                                       |                                                                               | min | 45   | 55  | 70  | 90 | 120  | ns |  |

| $t_{ m AVQV}$       | $t_{ m ACC}$      | Addresee to Output Delay                                              | $\overline{\text{CE}} = V_{\text{IL}}$ $\overline{\text{OE}} = V_{\text{IL}}$ | max | 45   | 55  | 70  | 90 | 120  | ns |  |

| tELQV               | $t_{\rm CE}$      | Chip Enable to Output Delay                                           | $\overline{\mathrm{OE}}{=}V_{\mathrm{1L}}$                                    | max | 45   | 55  | 70  | 90 | 120  | ns |  |

| $t_{\rm GLQV}$      | $t_{\rm OE}$      | Output Enable to Output Delay                                         |                                                                               | max | 25   | 30  | 30  | 35 | 50   | ns |  |

| $t_{\mathrm{EHQZ}}$ | $t_{ m DF}$       | Chip Enable to Output High $Z$                                        |                                                                               | max | 10   | 15  | 20  | 20 | 30   | ns |  |

| $t_{\mathrm{GHQZ}}$ | $t_{ m DF}$       | Output Enable to Output High ${\cal Z}$                               |                                                                               | max | 10   | 15  | 20  | 20 | 30   | ns |  |

|                     |                   |                                                                       | Read                                                                          | min |      |     | 0   |    |      | ns |  |

|                     | toeh              | Output Enable Hold Time                                               | Toggle and<br>Data Polling                                                    | min | 10   |     |     |    | ns   |    |  |

| $t_{ m AXQX}$       | $t_{\mathrm{OH}}$ | Output Hold Time From<br>Addresses CE or OE Whichever<br>Occurs First |                                                                               | min |      |     | 0   |    |      | ns |  |

两处的电压基点表示如果低于下面的基点则为低电平,如果高于上面的基点则为高电平。处于两者之间的电压则根据器件的特性及其他,或者识别为高电平,或者识别为低电平。具体的电压将在后面的说明(DC 规定)中出现。

通常在波形下降阶段,处在下方的基点表示起始于确定了低电平那个时刻;而上方的基点则表示不能认为是高电平的那个时刻(根据器件,有时候也认为是可以识别为低电平的那个时刻)。一般情况下,时序规定都尽可能地严格。

现在,我们对上图中出现的 tRC、tOEH、tOH、tDF4 个参数加以说明。

#### ▲ tRC(读周期时间)

这是确定(稳定)地址的时间。通过数据手册我们了解到,由于该时间与 tACC(从地址到数据输出的时间)是同一的,所以采用通常的方法一般不会出现问题。

## ▲ tOEH(输出使能保持时间)

这是在刚进行完写操作的情况下,从/WE 成为高电平开始到/OE 成为低电平之间的时间规定。由于在数据手册上最小为 Ons, 所以可以解释为只要/WE 和/OE 不同时为低电平即可。

#### ▲ tOH (输出保持时间)

在/OE 信号恢复为高电平后,只要进行严格的测定,就可测出 DQ 输出仍在持续进行。从/OE 不是低电平开始到 DQ 不再输出正确的数据这一段时间就是 tOH。由于 Am29F010A 的这个时间最小为 0,所以一旦 OE 变成高电平,则就不可再相信数据的准确性。

在存储器存取时间较长的情况下,利用该参数,在读取数据之前,先将/0E 恢复为高电平来争取时间,这样的设计事例曾经出现过。但实践证明放弃这样的做法才是明智的。

### ▲ tDF (从/CE、/OE 到输出高阻抗)

/CE 或者/OE 成为高电平之后. 闪速存储器的 DQ 输出完全成为高阻抗所需要的时间就是 tDF。因为这一时刻中闪速存储器可能会持续输出某些数据, 所以, 如果此刻其他的驱动器以及缓冲器被启动,则可能会发生数据冲突。在缓冲器的方向控制方面, 如果是在/OE 与缓冲器的方向控制等同时进行的电路中,则需要对缓冲器的切换时间是否过早进行判断。

# ● 2.4.7 写周期的时序

写周期的详细情况将在后面进行描述,这里要说明的是,写周期在闪速存储器中利用/WE 的存取操作不是类似 RAM 那样的向指定地址的直接写人操作,而是通过指令对闪速存储器进行操作。与 NAND 闪速存储器相同,通过一连串的指令序列,可以进行编程(数据写人)和芯片擦除操作。

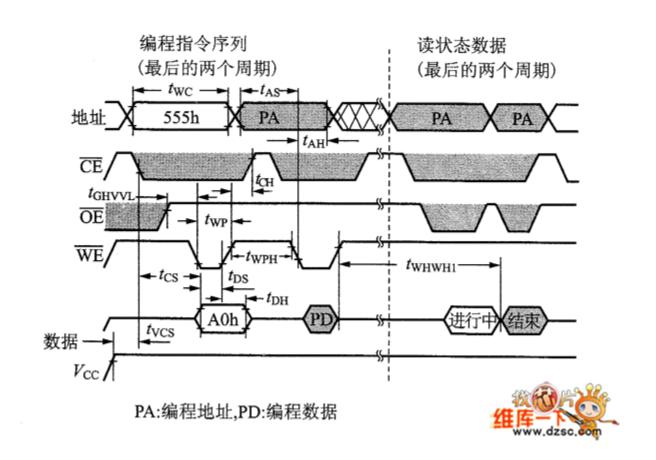

为此,时序图也以包括用于编程及擦除操作时间的形式被记录。图 1 为编程操作,图 2 为擦除操作。

图 1 编程操作

图 2 擦除操作

另外,在图中,如编程操作,是通过向 555h 写人 A0h、然后给予 PA(编程地址)和 PD(编程数据)的写人方法。但实际上,在访问 555h 之前,就进行几次写入操作,闪速存储器将此识别为编程操作。关于这种顺序将在以后详细说明。如果将该过程全部写下来,将会占据非常大的篇幅,因此省略大部分,只对最后部分进行说明。擦除操作也以相同的形式进行说明。

由于编程及擦除的内部操作相当花费时间,因此,需要从闪速存储器中取出其状态等,以便 CPU 检验操作是否结束。图的右半部分描述的就是这个验证操作。

无论怎样的操作时序,作为写操作基本上都是相同的,我们在说明编程操作之后,将简单地描述擦除时序。

### ■ 编程操作

首先,我们先看如图 1 所示的编程操作。因为时序规定的线太多,可能看起来非常复杂,但只要按照顺序追踪下去,就不会觉得困难。基本的时序思路刚才已经概括说明。

## ▲ t<sub>vcs</sub> (Vcc建立时间)

由于闪速存储器在内部具有对来自主机的指令进行解释的定序程序,因此电源一旦达到额定电压值,则立即不能进行存取。电源达到额定电压值之后到发出最初的指令之前,必须获得的时间就是tvcs。Am29F010A的这个时间为50μs。

通常,作为CPU的外部记忆加以使用的时候,一般都具备加电重启电路。电源接通后,解除CPU的复位,CPU到开始最初的存取一般都需要相当长的时间。因此,出现问题的时候较少,但在使用闪速存储器写人器的情况下,都在电源引脚上准备半导体开关等,插拔插座时关闭电源,在开始存取时,进行接通电源的操作。为此,在电源控制板上接通电源后,必须经过达到额定电压值所需要的时间+50 µ s 以后,才能访问闪速存储器,这是需要注意的地方。

### ▲ tCS (/CE 建立时间)

/WE 写控制的情况下,/CE 需要提前于/WE 有效,这个提前的时间就是 tCS。因为时序规定最小为 0ns,所以也就意味着它不能为负值,也就是/CE 不可能在/WE 之后有效。如果/CE 在/WE 之后有效,就 成为了/CE 写控制。

## ▲ tWC (写周期时间)

这是在写操作中确定地址的时间。Am29F010A-55 需要保持 55ns 以上的时间。

## ▲ tGHWL (读恢复时间)

这是在写周期的前面为读周期的情况下,/OE必须在/WE多少时间之前无效的规定。

## ▲ twp (写低电平脉冲宽度)

规定了/WE 有效的期间。Am29F010A-55 最小为 30ns。

## ▲ tDS (数据建立时间)

在向闪速存储器中进行写操作时,虽然数据是在/WE 的上升阶段被提取。但是对于正确数据的锁定,需要在/WE 上升之前确定数据(DQ0~DQ7),这个时间就是 tDS。Am29F010-55 为 20ns,所以需要在 20ns 以上的时间之前确定数据。

## ▲ tDH (数据保持时间)

这是在/WE 上升后必须保持数据被确定的时间。以前根据器件内部的情况,某种程度上需要这个时间。但在最近的器件中. 这个时间为 0。也就是说,到/WE 上升,数据大多能被保持。Am29F010A 的tDH 就为 0ns。

## ▲ tAS (地址建立时间)

将写操作时的地址提取到闪速存储器是在/WE 的下降时刻,所以在达到该下降时刻之前必须确定地址。tAS 表示在/WE 下降之前的多少时间前确定地址需要。

Am29F010A的 tAS为 0,因此,最慢也要在/WE的下降时刻确定地址。

## ▲ tAH(地址保持时间)

虽然写操作时的地址是在/WE 下降时锁存的,但这也与 tDH 相同,需要规定持续保持的时间。 Am29F010A-55 需要的 tAH 时间为 45ns。

### ▲ tWPH (写高电平脉冲宽度)

这是/WE 无效后到下一次/WE 有效的时间。Am29F010A 最少需要 20ns 的时间,所以连续存取时必须获取超过 20ns 的间隔时间。

### ▲ tWHWH1 (字节编程操作时间)

在进行编程操作时,虽然用最后的写操作指定写人地址及数据,但闪速存储器并不是在完成写操作的同时,完成向闪速存储器单元的写入。一看芯片内部的框图就可知道,在闪速存储器内部具有状态控制器及写入电压生成电路,编程指令只不过是状态机的启动脉冲向单元发出开始写人操作的指示而已。写人电路工作直到实际完成向存储器单元的写人操作,这一段时间就是 tWHWH1。Am29F010A 的 tWHWH1 时间为 7 μ s,但因为这毕竟是典型值,所以多少存在一些变化。判断是否真正完成写入操作不是通过时间管理,而是必须根据数据读的状态验证来进行。

在 tWHWH1 期间,如果 CPU 针对闪速存储器进行数据读操作,则在 DQ 中将出现内部的操作状态,这是理所当然的事情。只要完成读取就成为一般的读周期,数据就会被读出。图中表示了最后切换的时序。

关于具体的状态内容等, 我们将在后面进行说明。

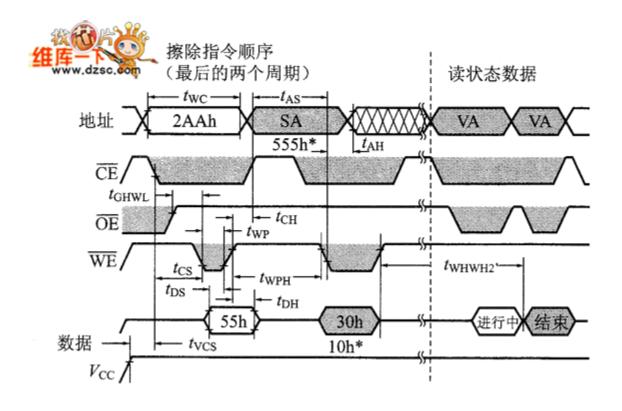

## ■ 擦除操作

#### ▲ tWHWH2

擦除操作与编程操作一样,由主机发出一连串的指令序列,器件从识别出擦除指令的时刻起,开始内部的操作。

写操作方面的时序与编程操作完全相同,但与编程操作相比,擦除操作却需要较长的时间。该时间就是 tWHWH2。Am29F010A 为 1s,该值也是典型值,实际上与编程操作相同,也将查询状态进行验证。

# ●2.4.8 闪速存储器指令

通过地址与数据特定组合的若干次写人序列,向闪速存储器发出指令。利用这样的序列,防止由于编程错误及开通电源的暂时不稳定等因素所引发偶然擦除及写人操作。

Am29F010A的指令定义如表所示。例如,当编程指令(向闪速存储器特定地址写入数据)下达时,如下所述:

- ①向 555h 地址写人 AAh;

- ②向 2AAh 地址写人 55h;

- ③向 555h 地址写入 A0h;

- ④向希望写人地址(PA)处写人希望写入的数据(PD)。

表 Am29F010A 的指令定义

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      |      |      |      | 总    | 线          | 周    | 期    |      |      |      |          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|------|------|------|------|------------|------|------|------|------|------|----------|

| Parish and   | 指令顺序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 周期 | 第1   | 次    | 第2次  |      | 第3次  |            | 第4次  |      | 第5次  |      | 第6次  |          |

|              | 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | Addr | Data | Addr | Data | Adde | Data       | Addr | Data | Addr | Data | Addr | Data     |

| Read         | and the second s | 1  | RA   | RD   |      |      |      |            |      |      |      |      |      |          |

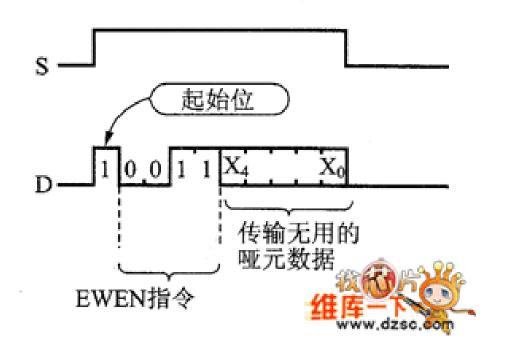

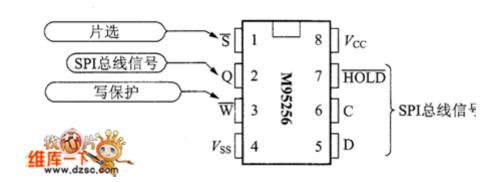

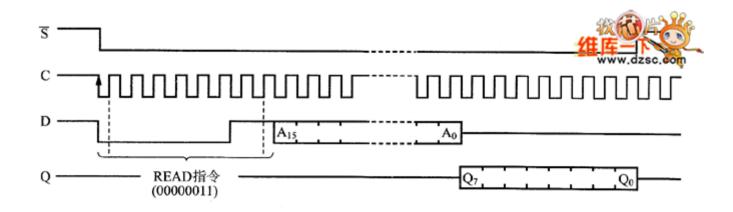

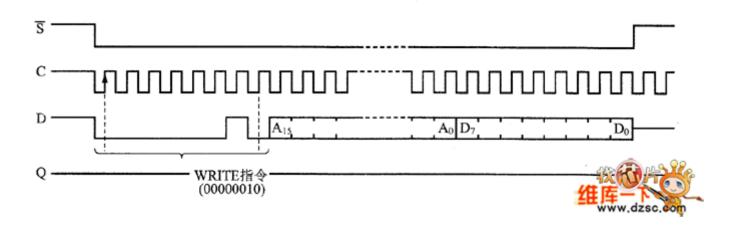

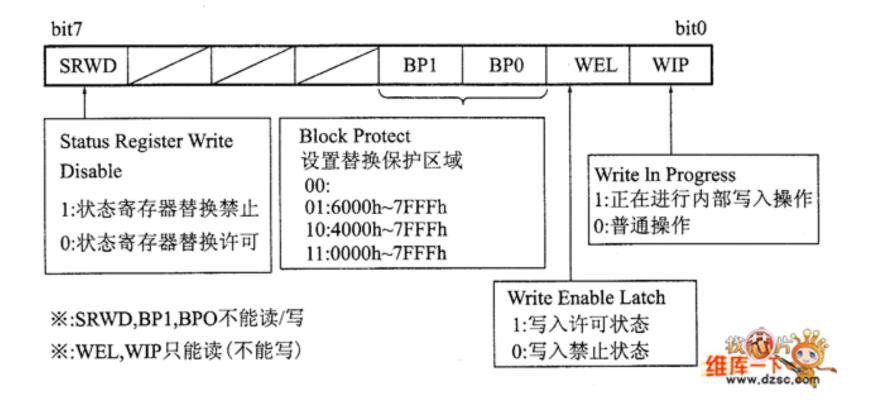

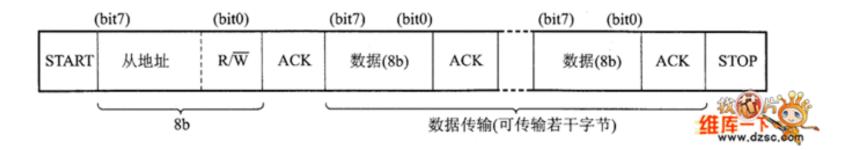

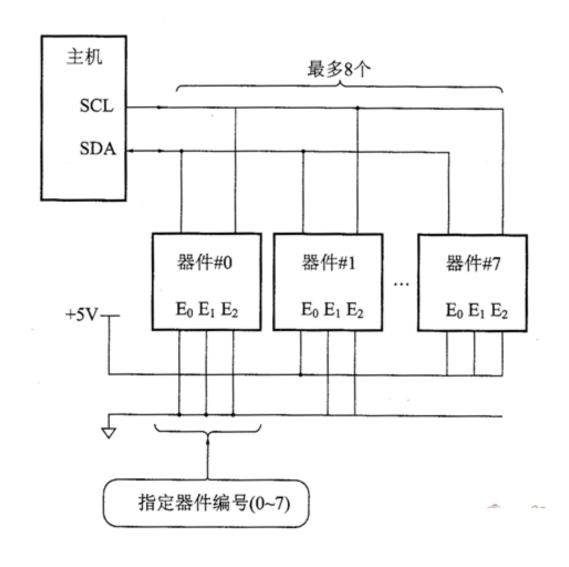

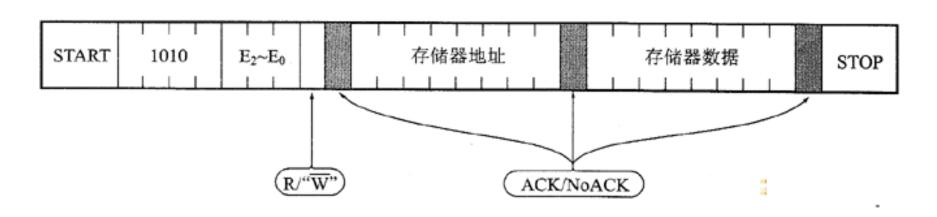

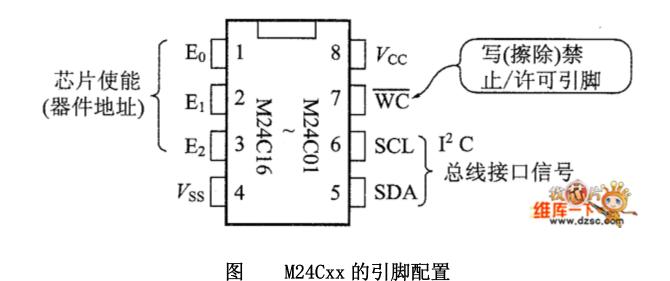

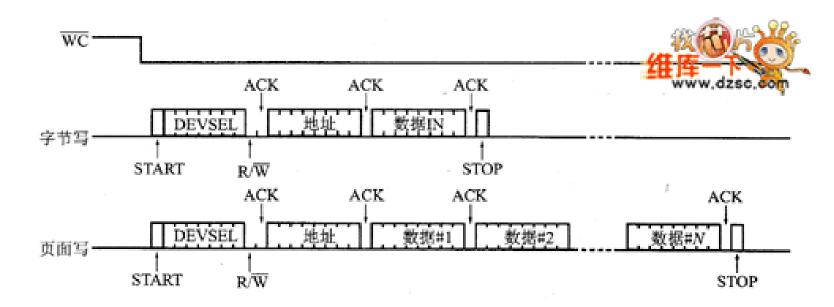

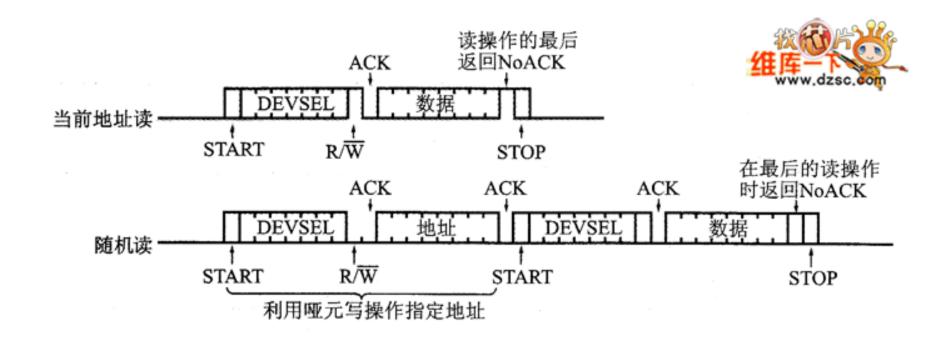

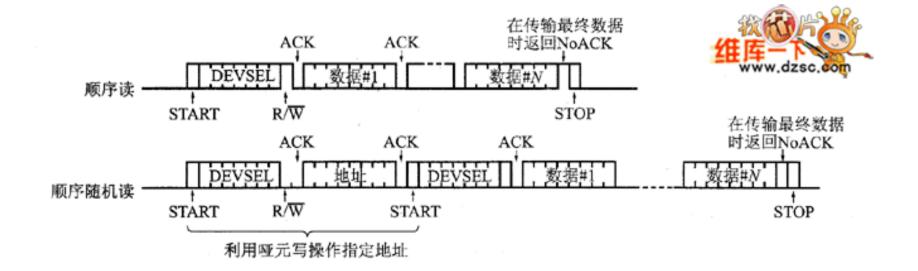

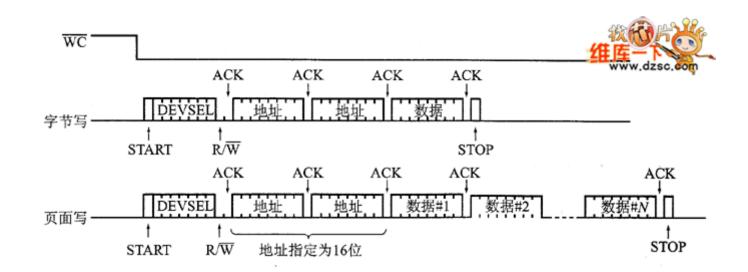

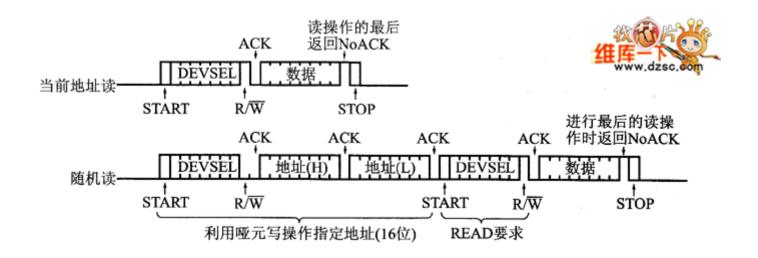

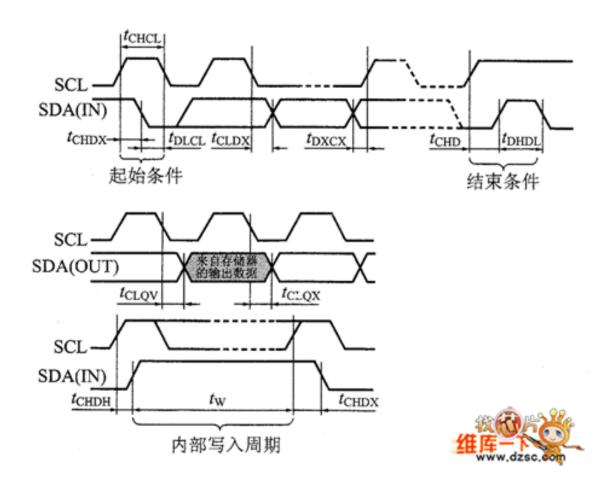

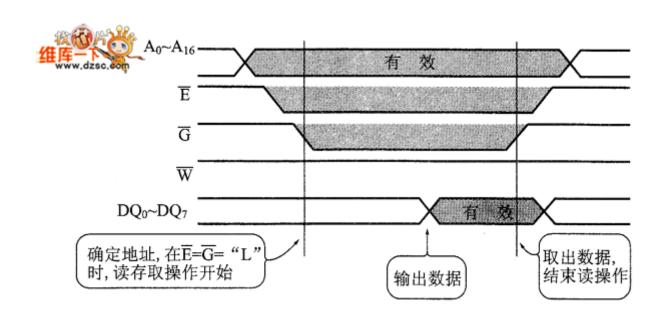

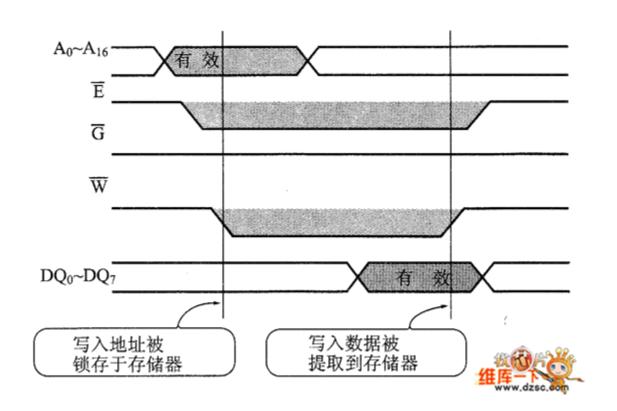

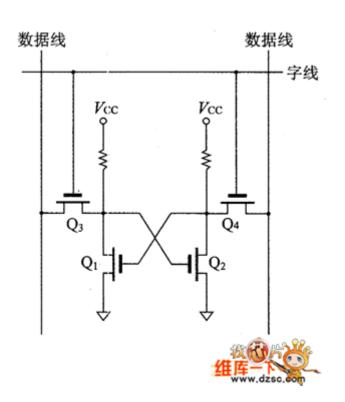

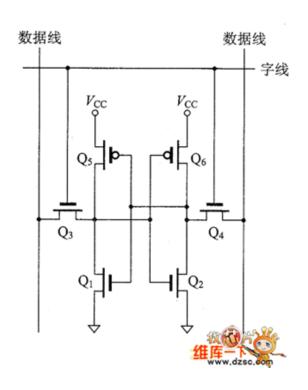

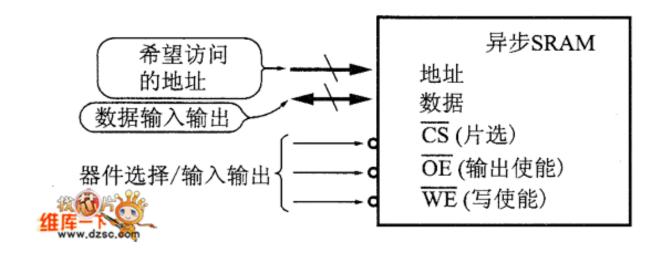

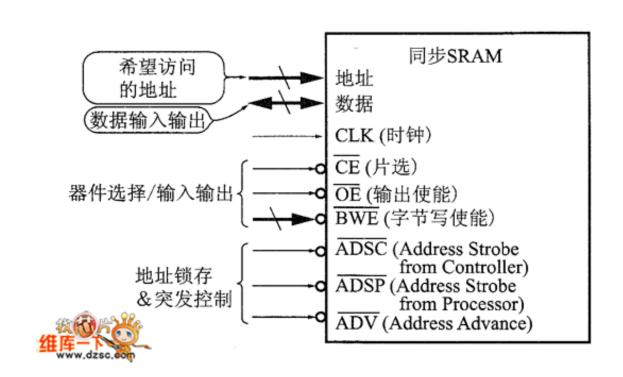

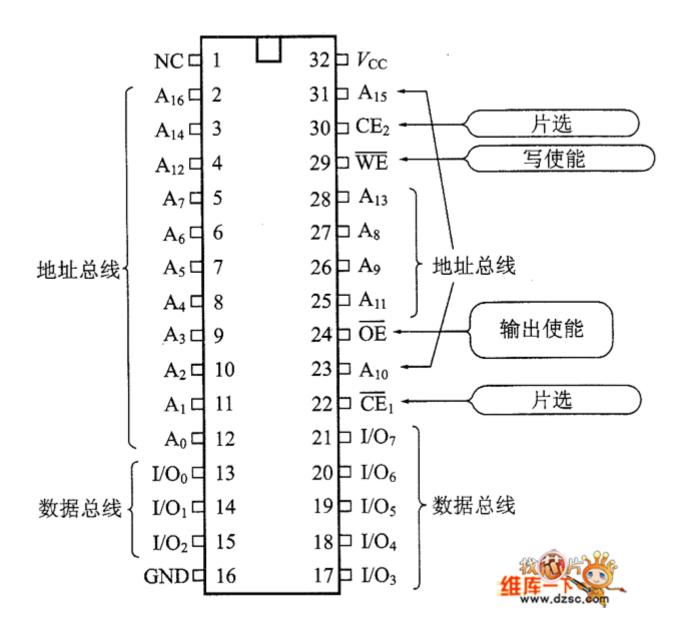

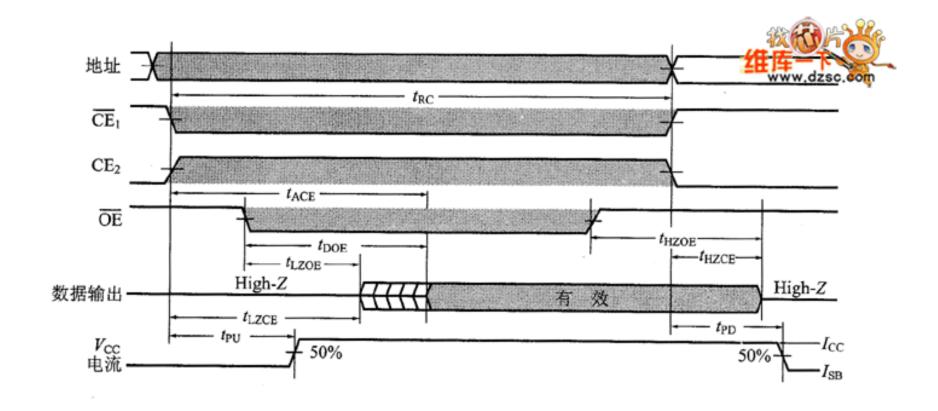

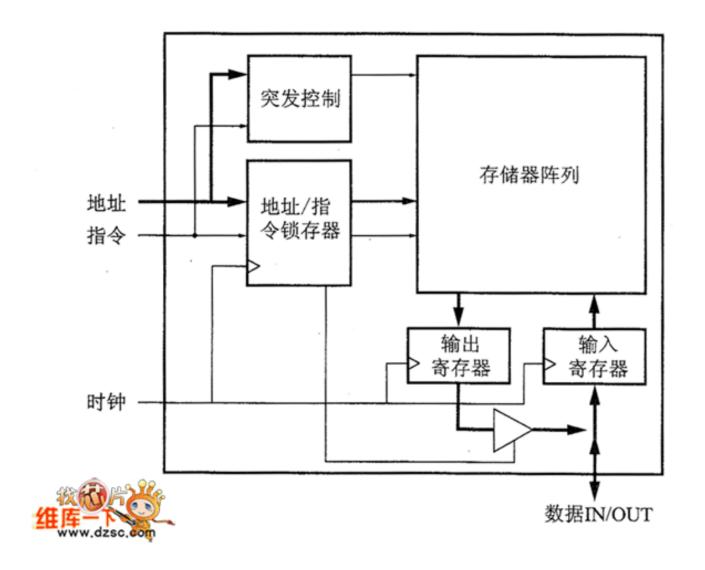

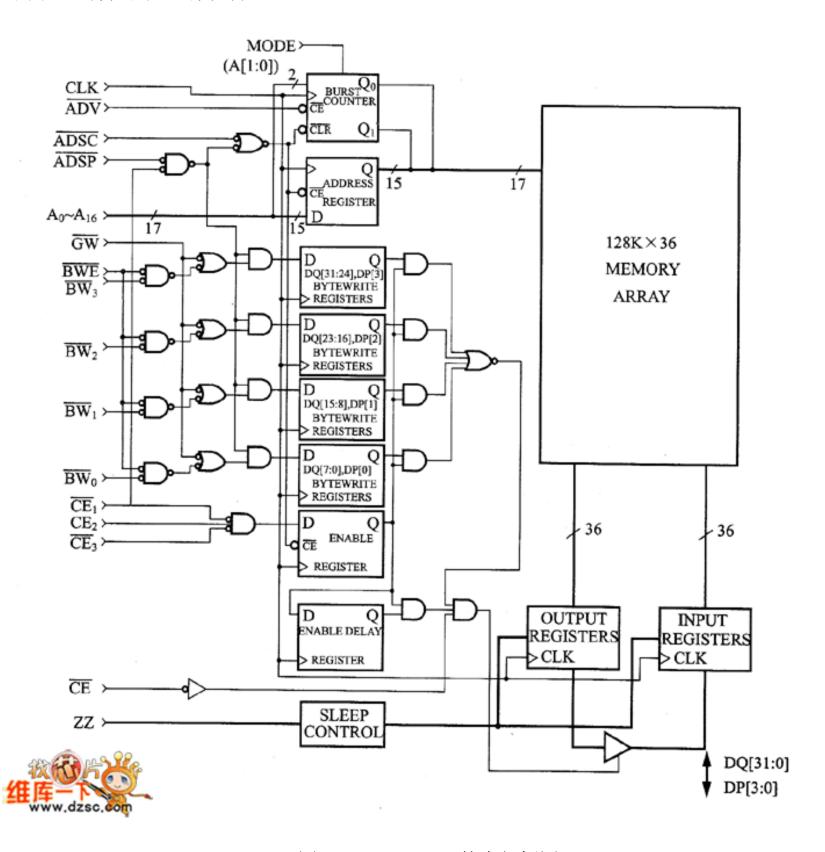

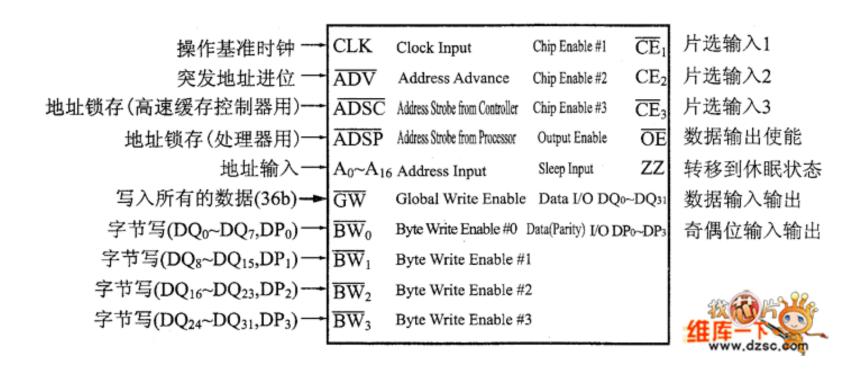

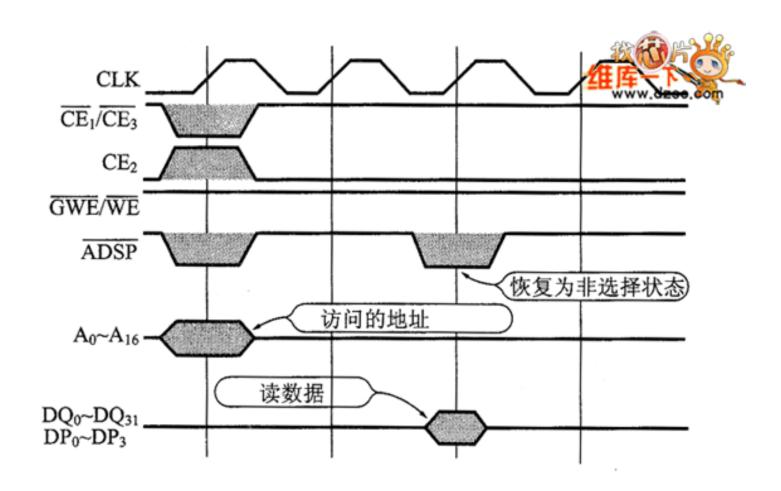

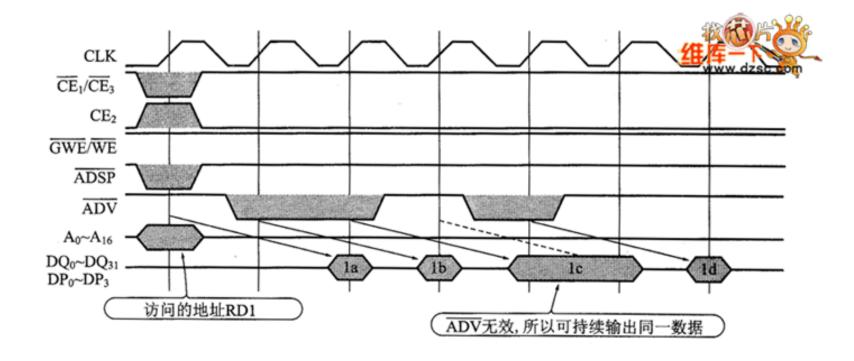

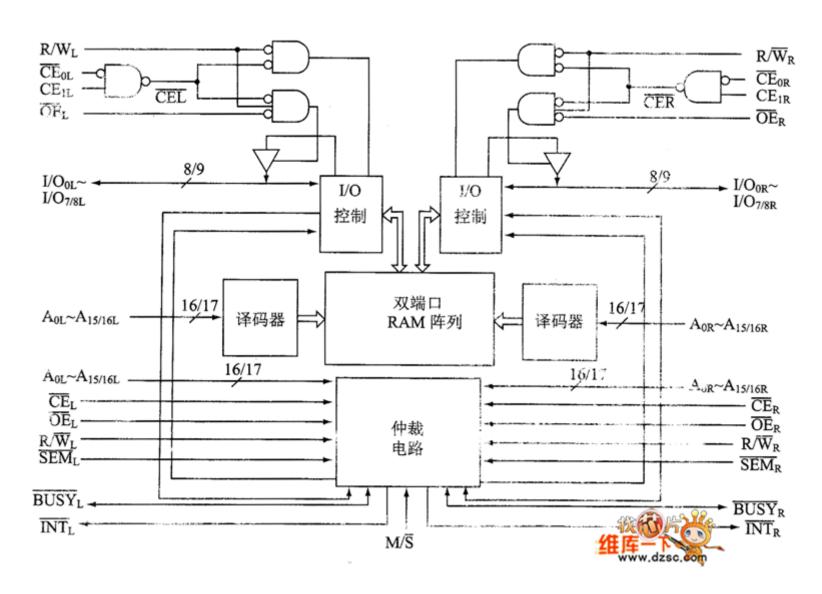

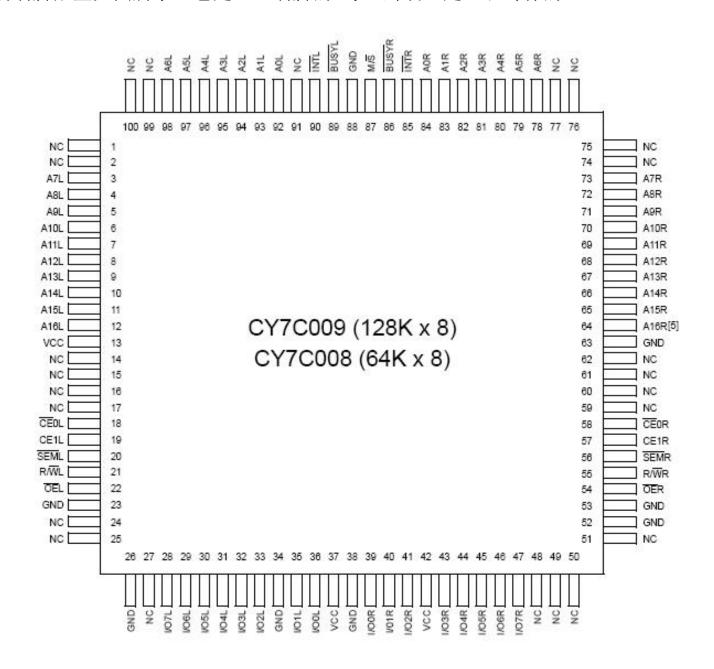

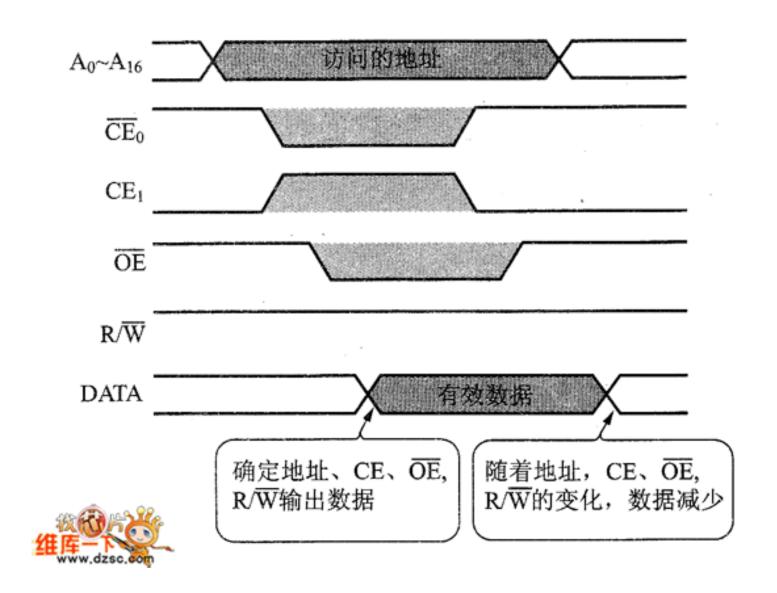

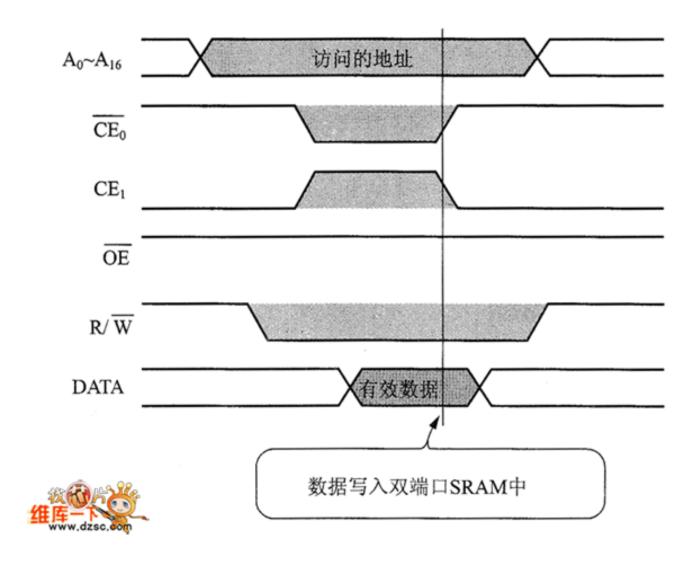

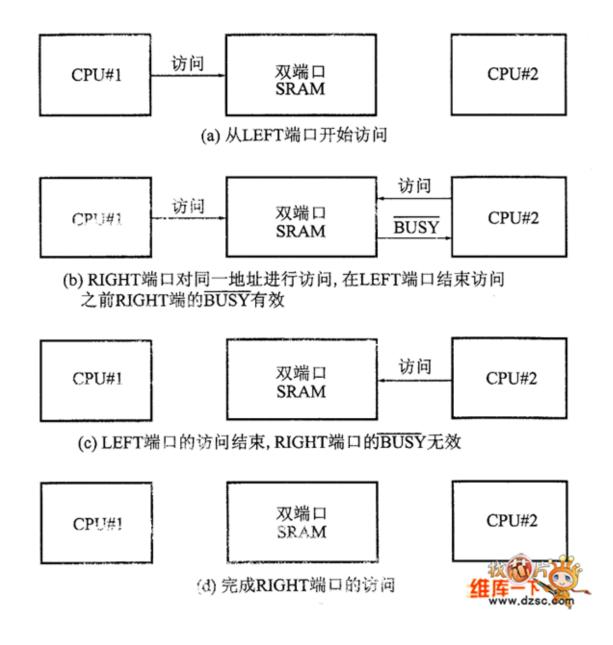

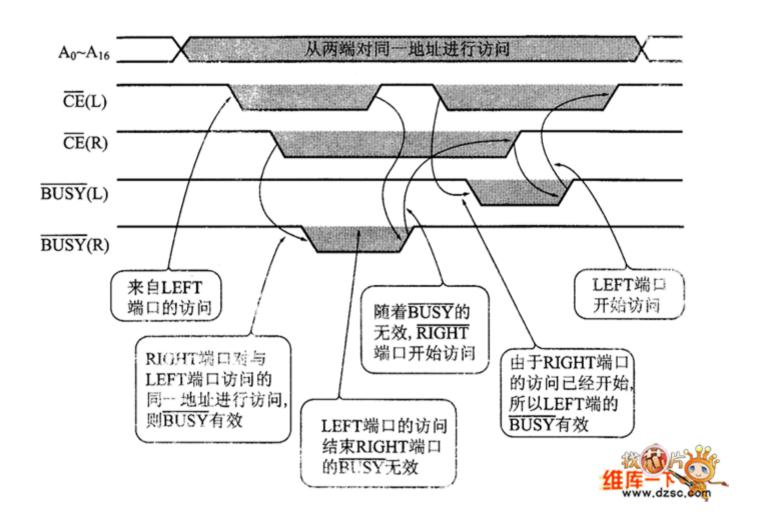

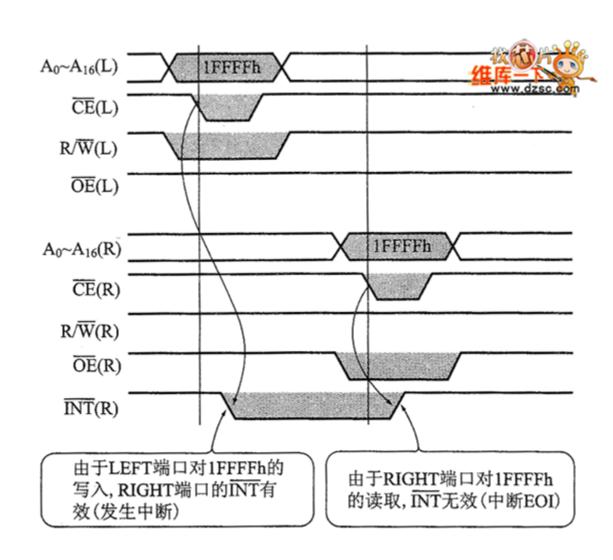

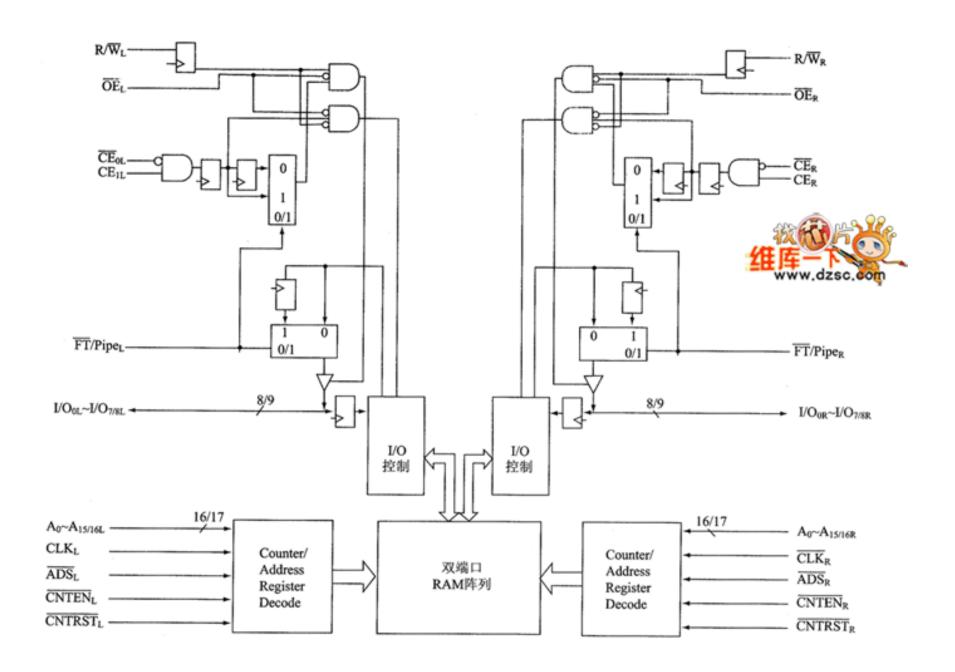

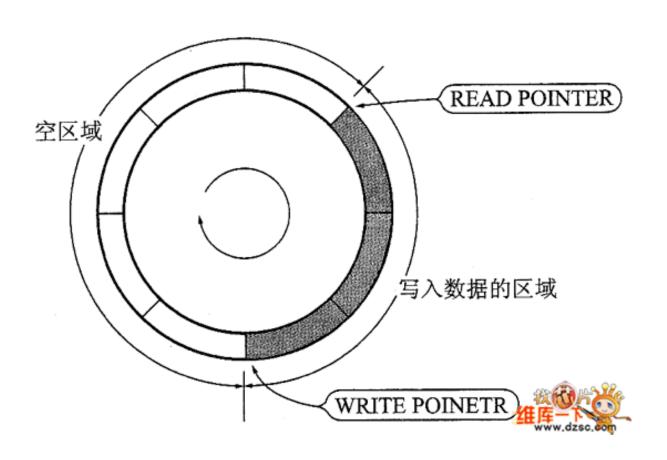

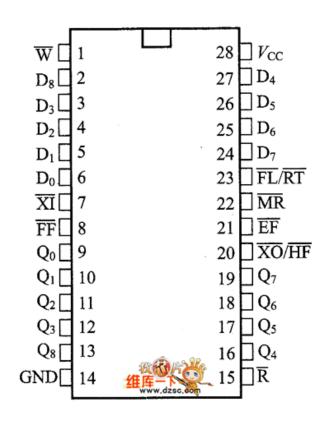

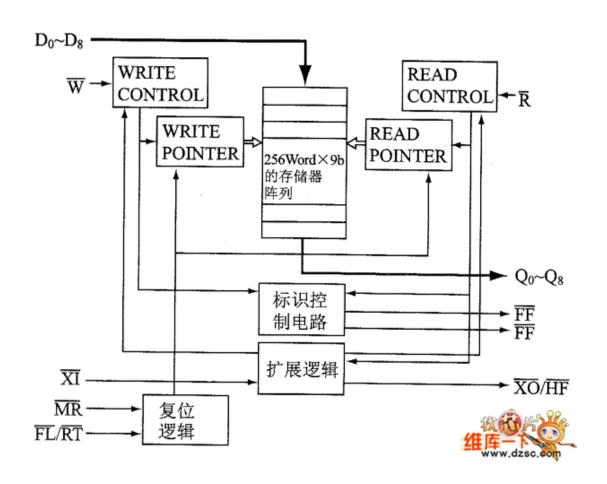

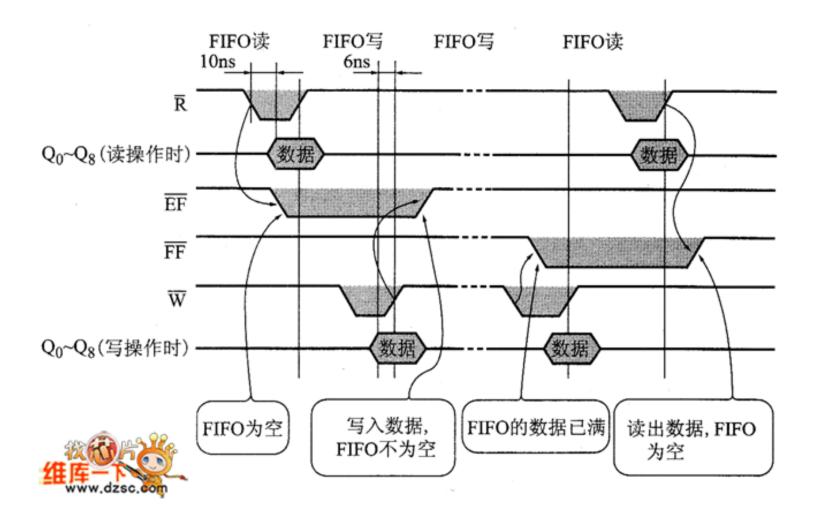

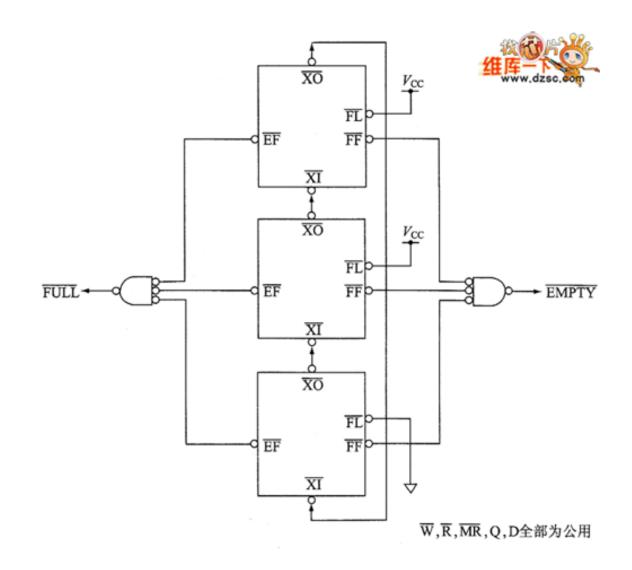

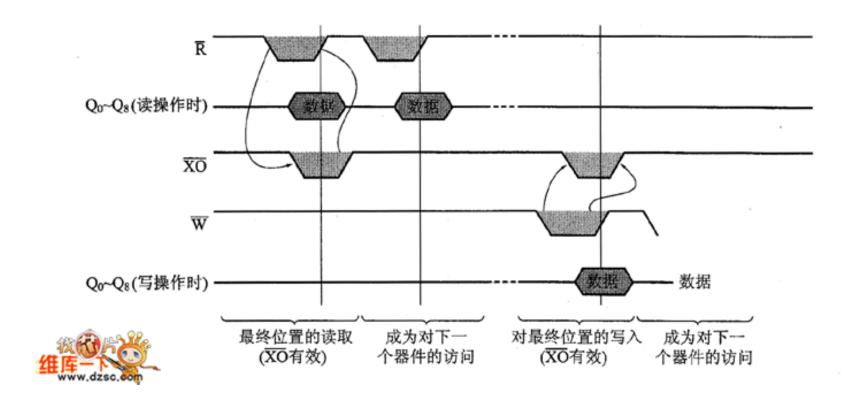

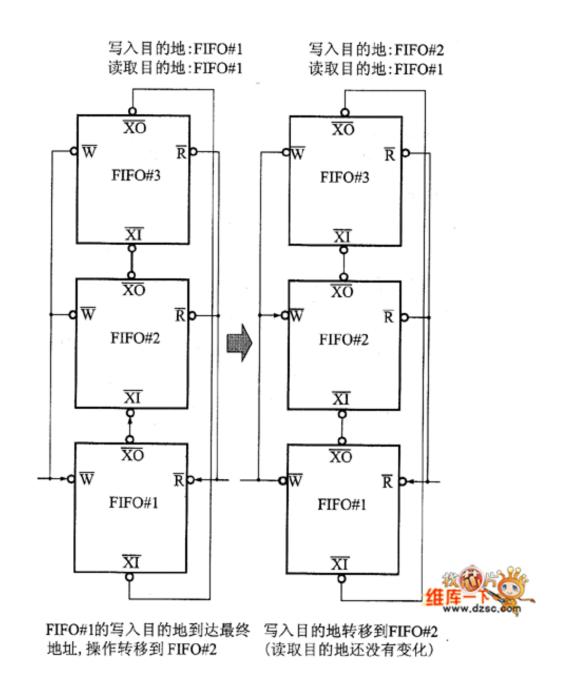

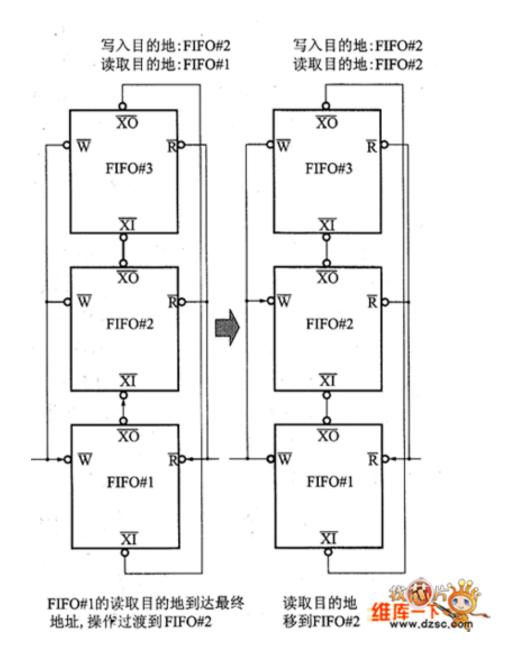

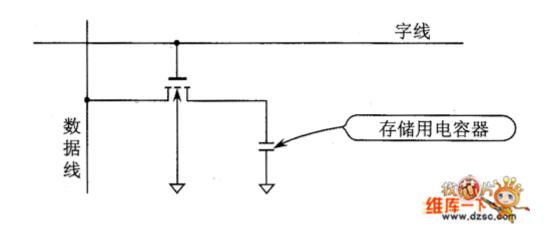

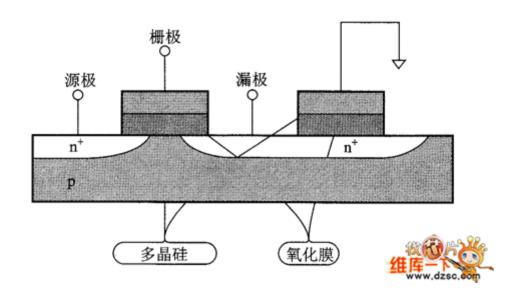

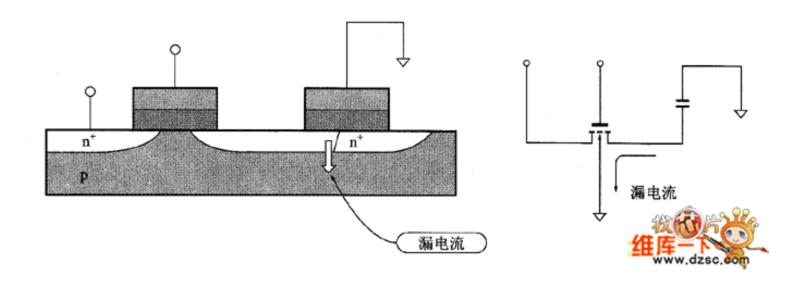

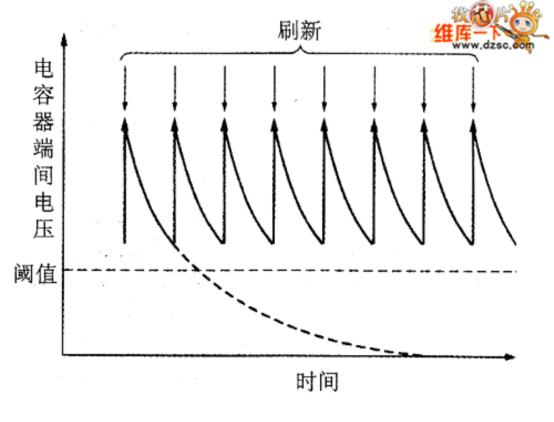

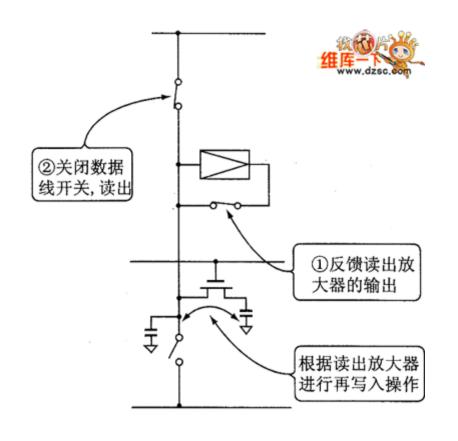

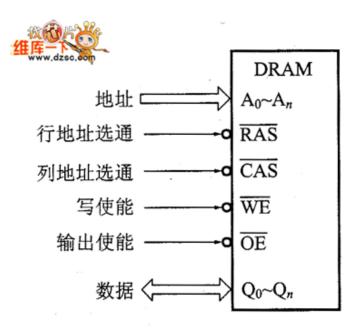

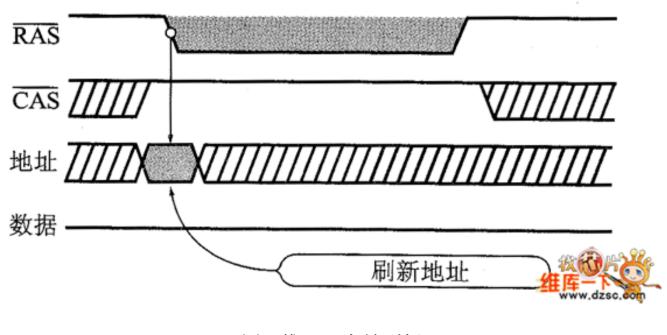

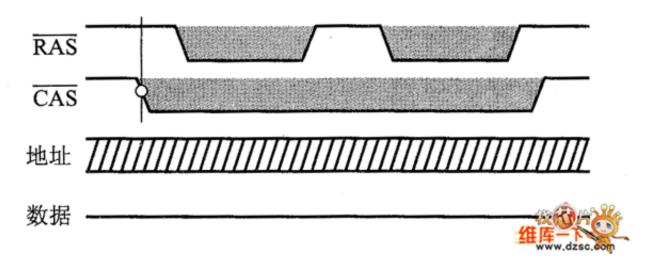

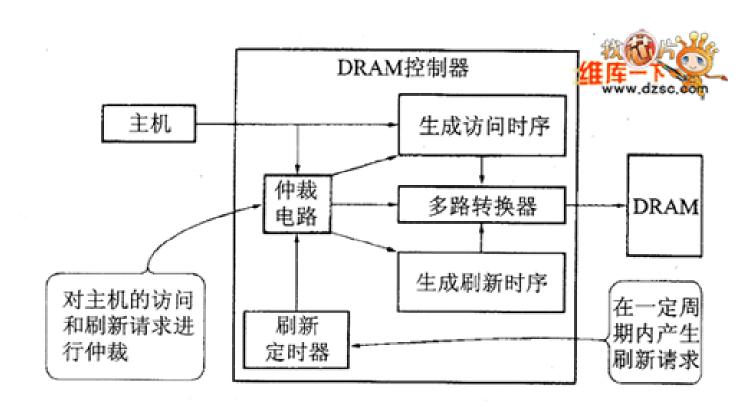

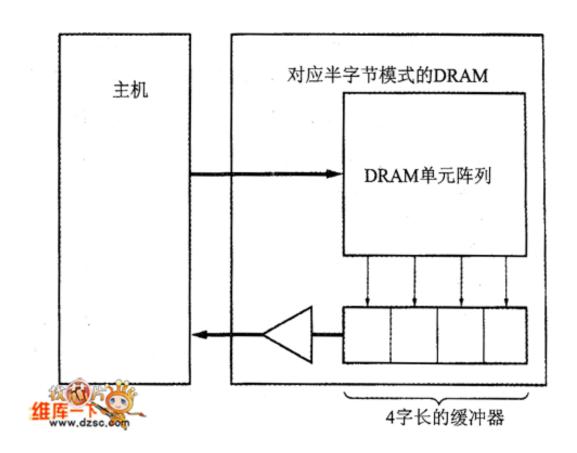

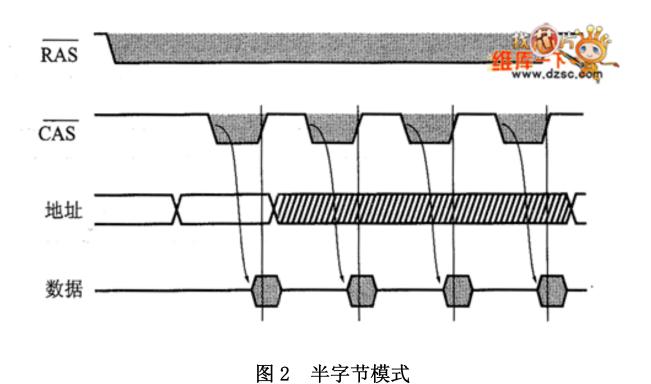

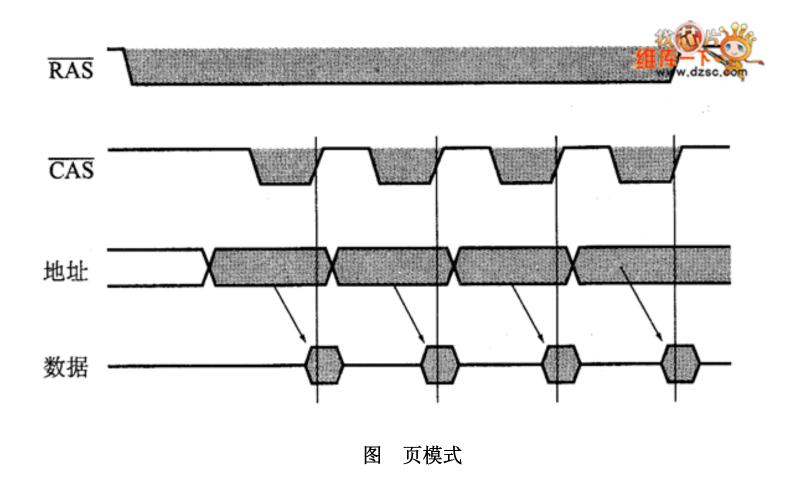

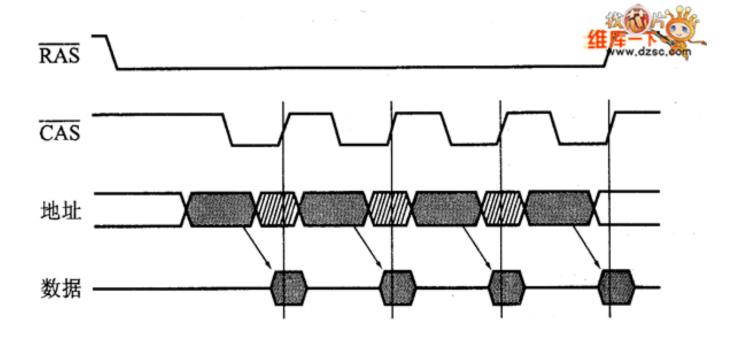

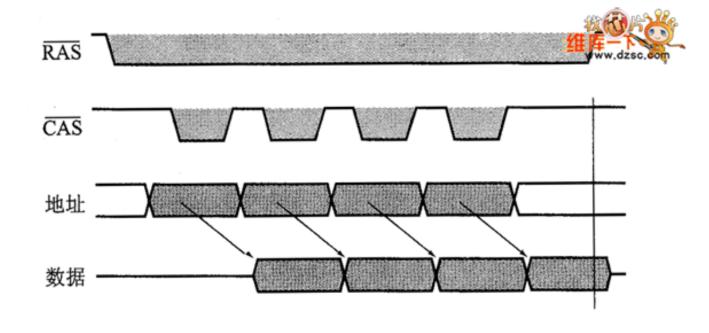

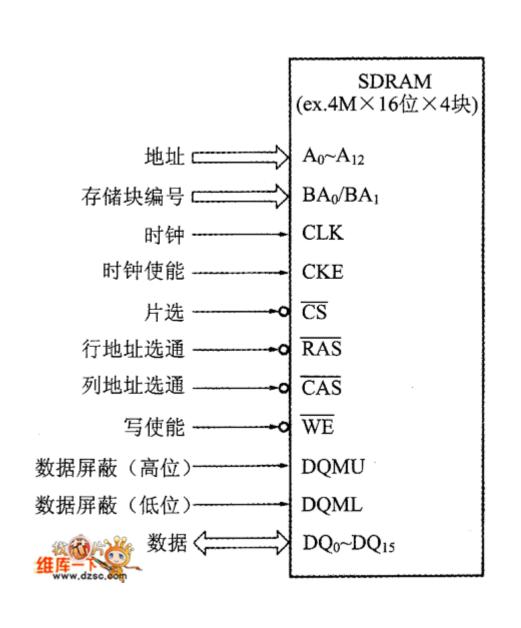

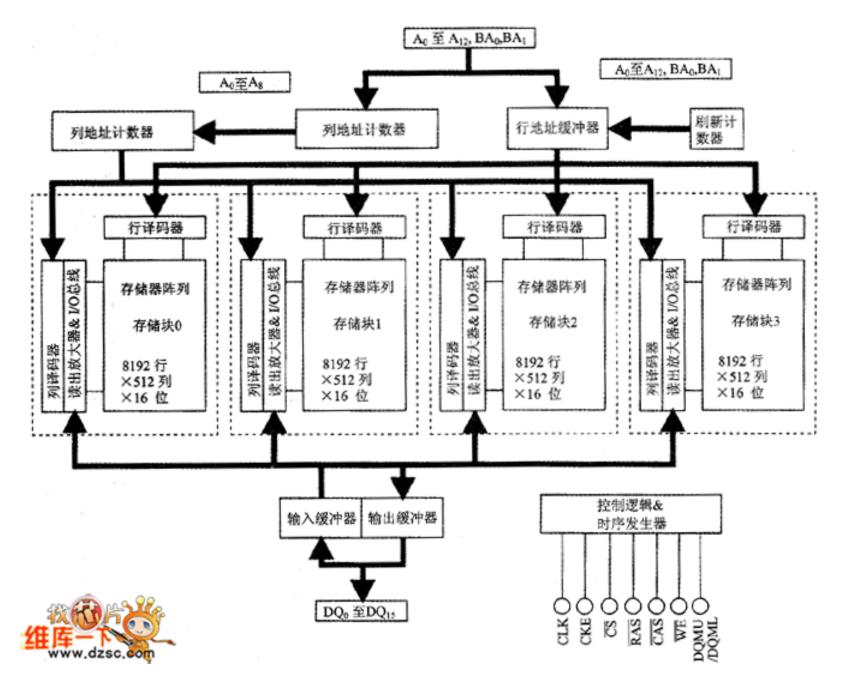

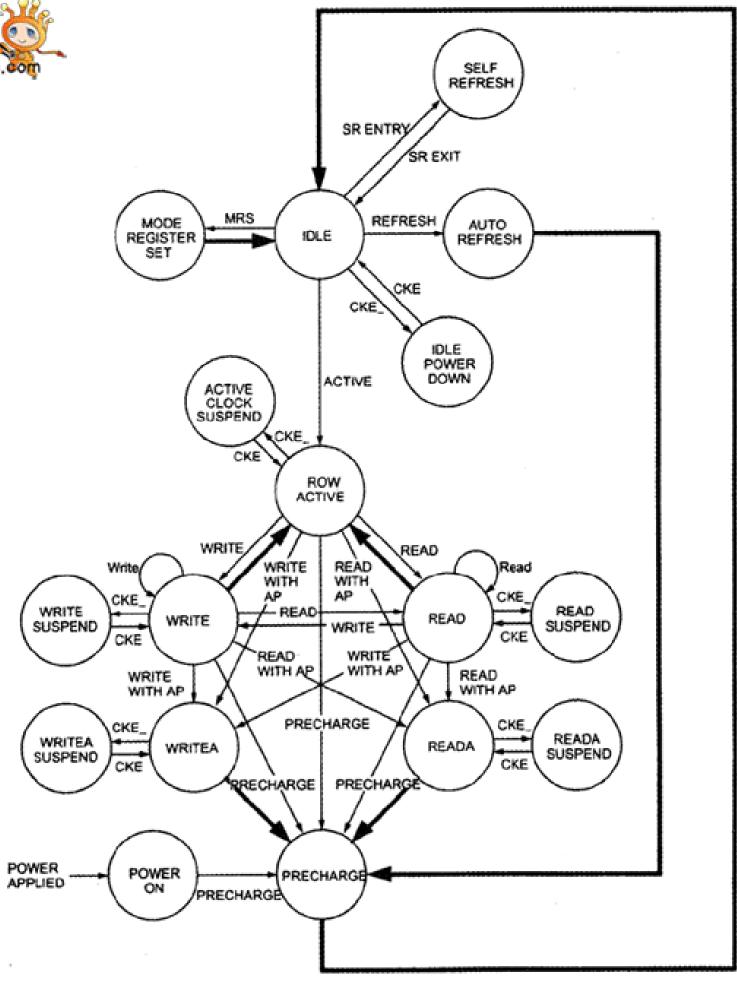

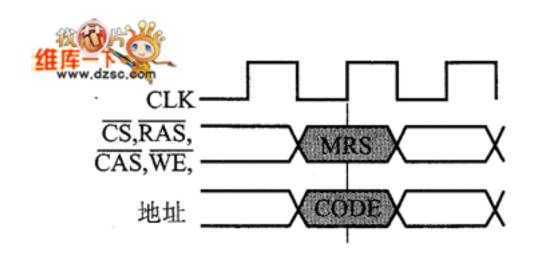

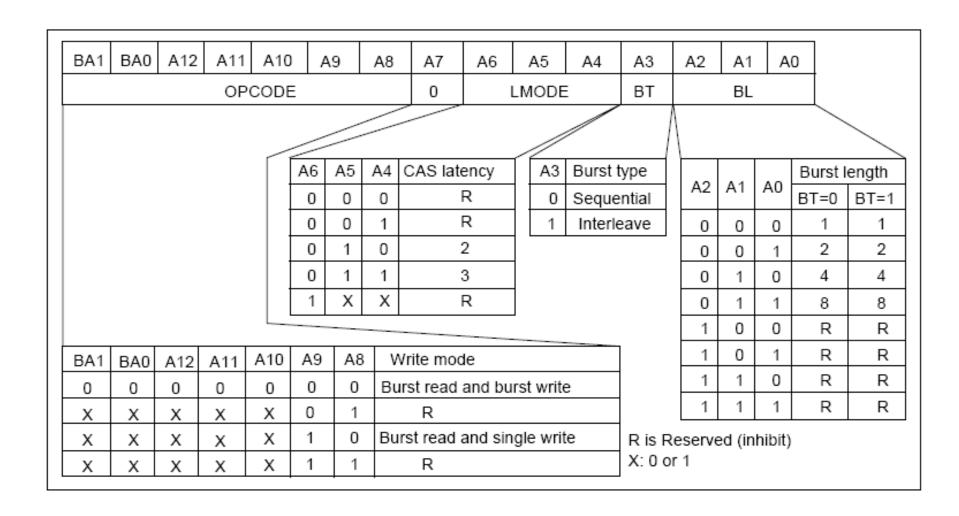

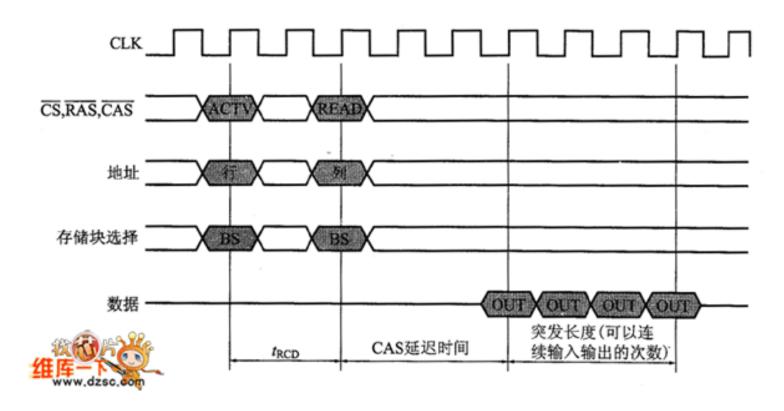

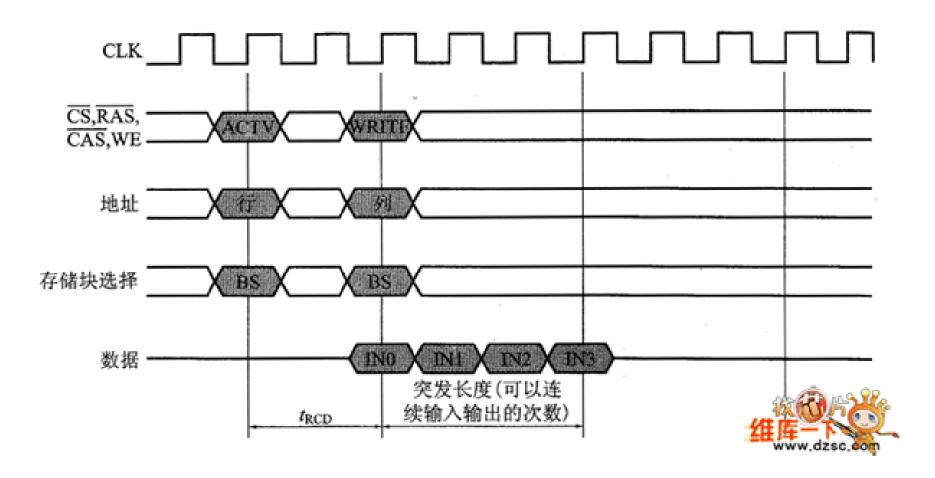

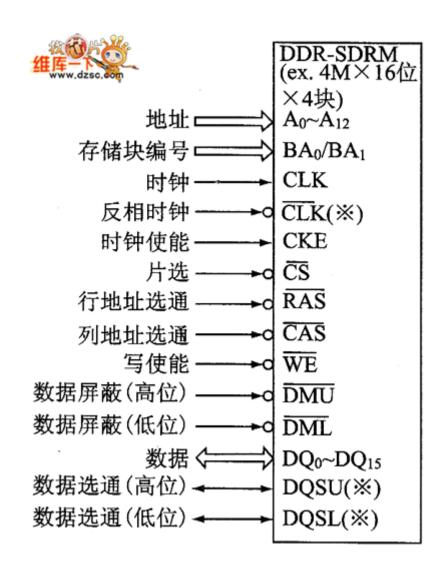

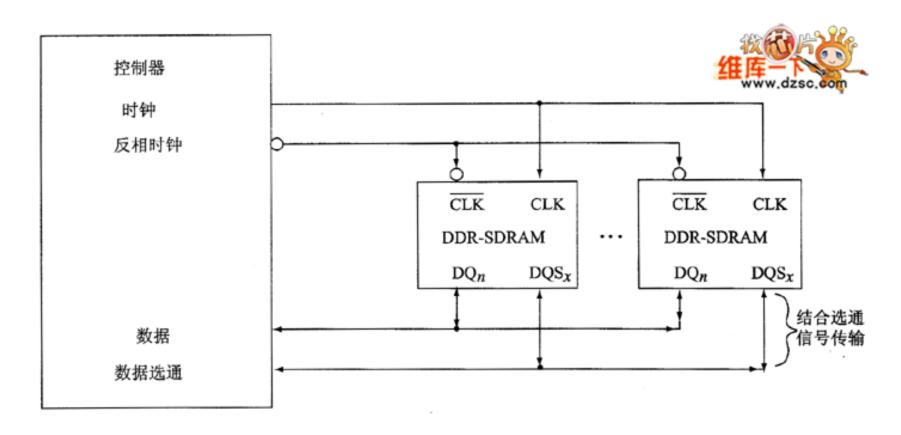

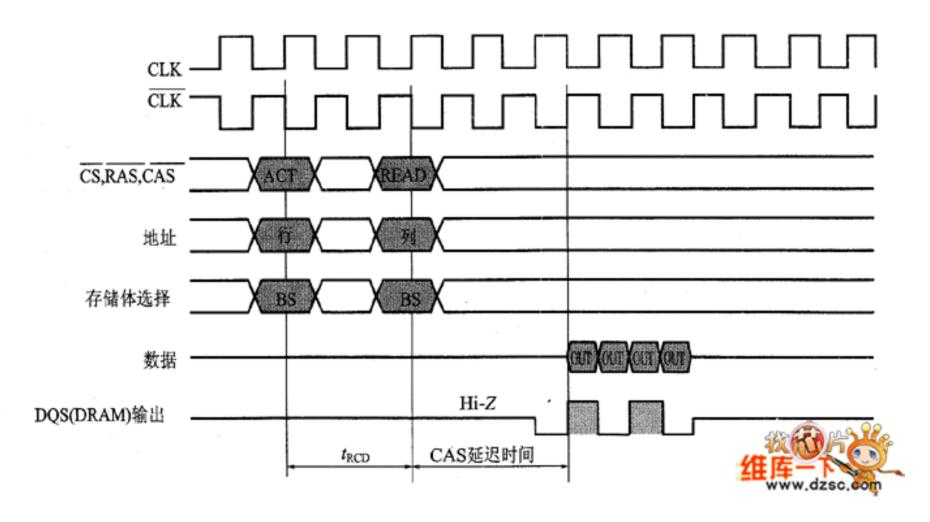

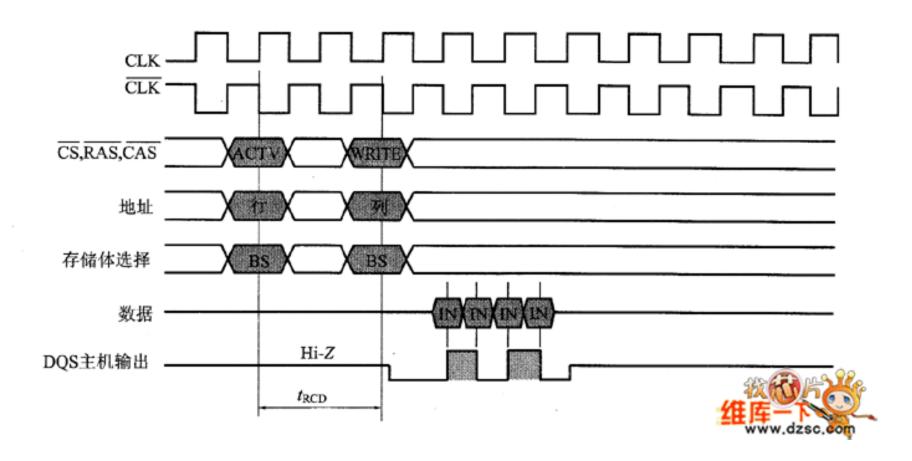

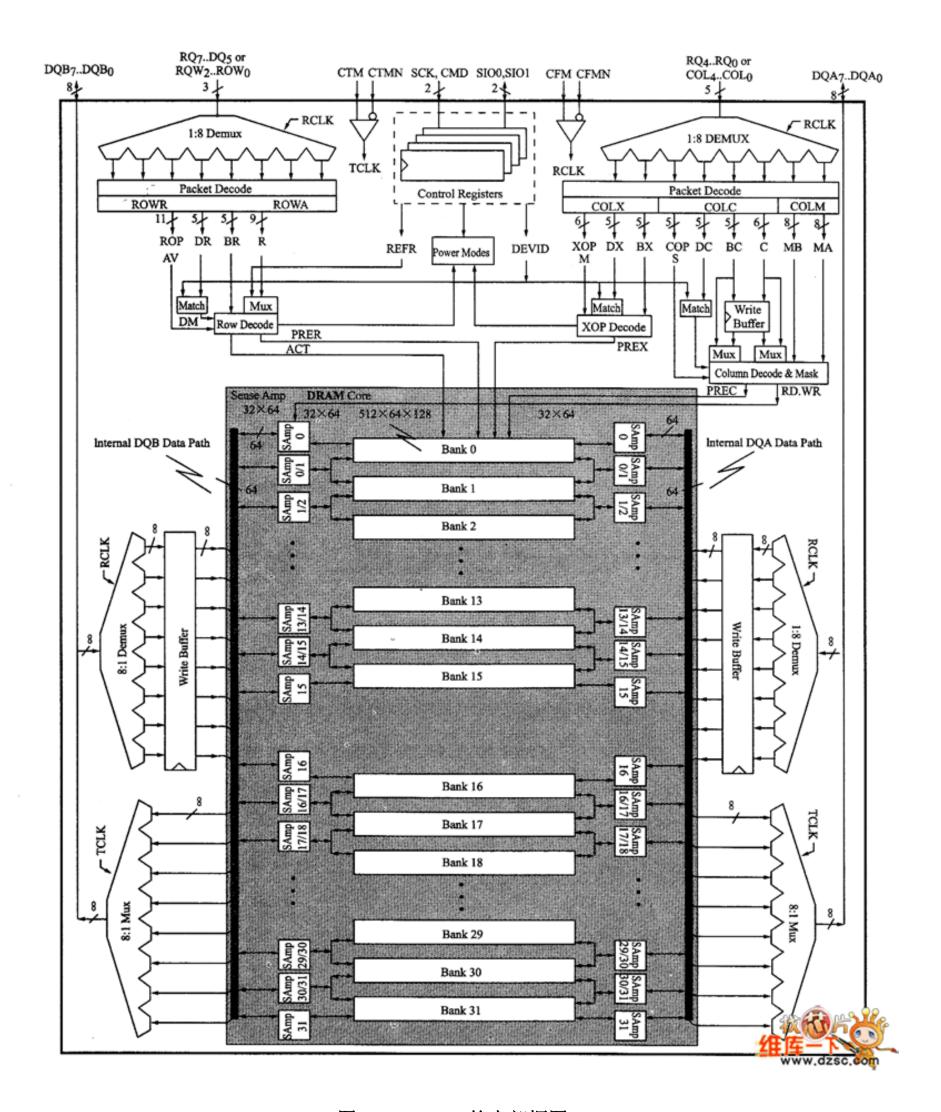

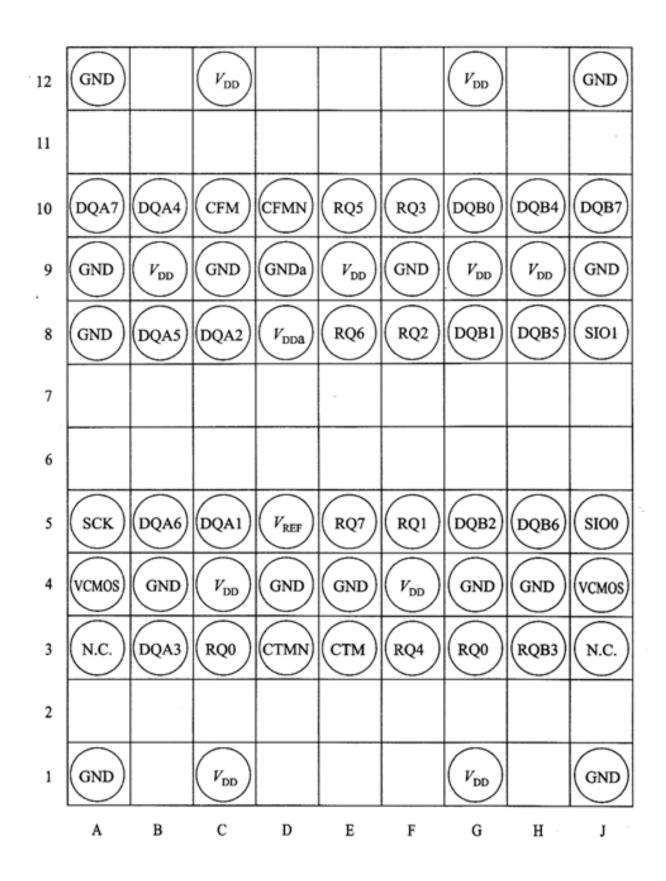

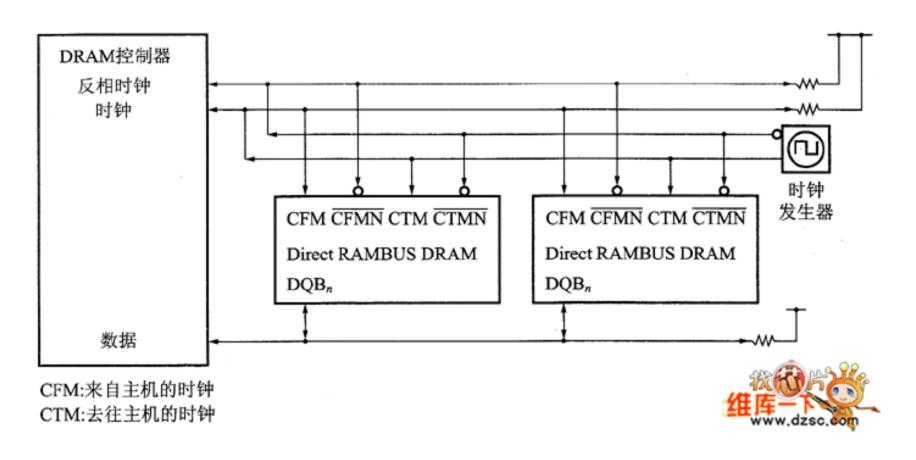

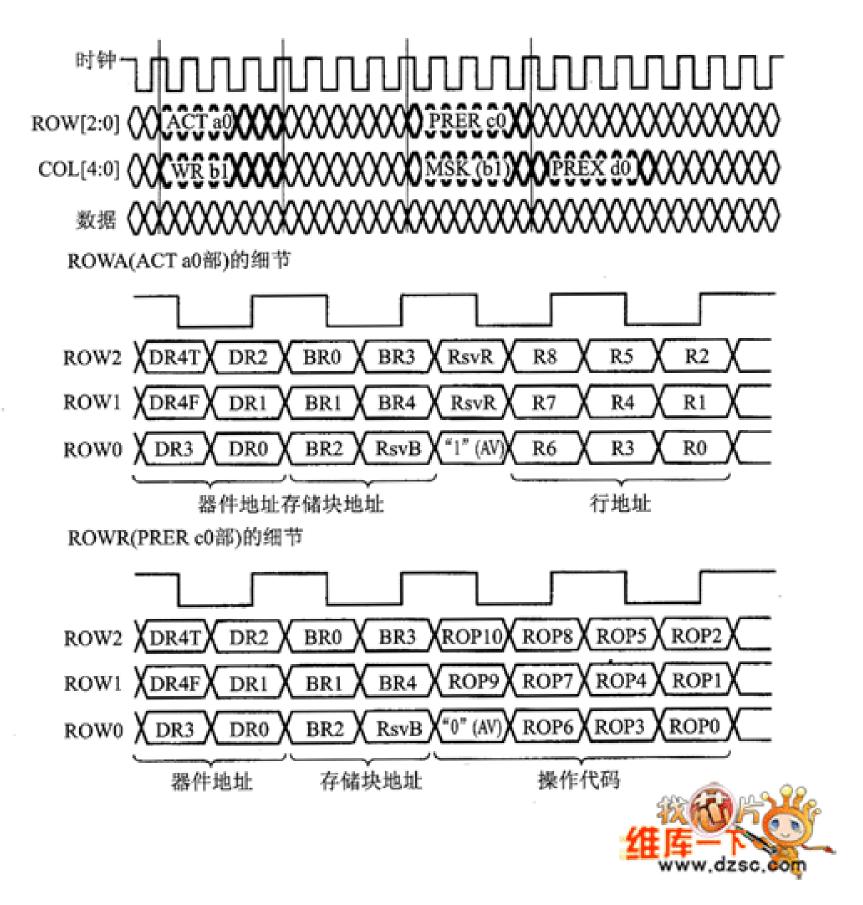

| Reset        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1  | XXXX | F٥   |      |      |      |            |      |      |      |      |      |          |